作者:赵瑜斌Robin,来源:IC后摩号

由于深度学习(DL)模型规模的不断增长,在大型单片芯片上实现用于深度学习的存内计算(IMC)面临面积、良率和制造成本方面的挑战。基于2.5D芯粒堆叠的架构可集成小芯粒扩大成一个大型计算系统,广泛用于加速大型深度学习模型。

3.5D堆叠芯片模型:支持存内计算加速同时具有多物理场设计挑战

该类系统设计中,需要在系统设计阶段早期评估性能,并探索不同的架构配置,以支持多种深度神经网络、不同的架构配置以及高效的设计空间探索;并通过对跨不同数据集的先进深度神经网络进行基准测试,获得评估端到端系统的有效性。

Content

DNN芯粒存内计算设计需求

深、宽、多分支DNN设计需求

仿真器

多层架构与仿真

基准测试方法

划分与映射

电路与NoC

NoP

DRAM访问

仿真结果与小结

1. 需求

具有更深、更宽和多分支结构的深度神经网络(DNN)为各种应用提供了最先进的性能。然而,深度神经网络复杂性的增加导致计算和内存需求的增加,从而降低了硬件性能。基于存内计算的架构可以通过将深度学习操作嵌入到存储阵列中来支持这些深度神经网络模型,实现并行计算和高存储密度。

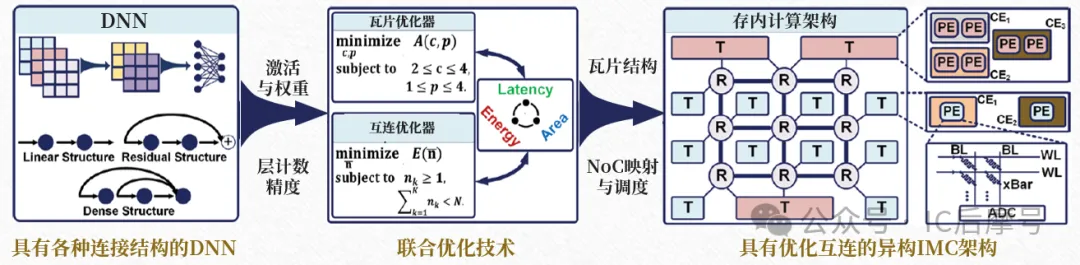

一种先进的DNN优化步骤

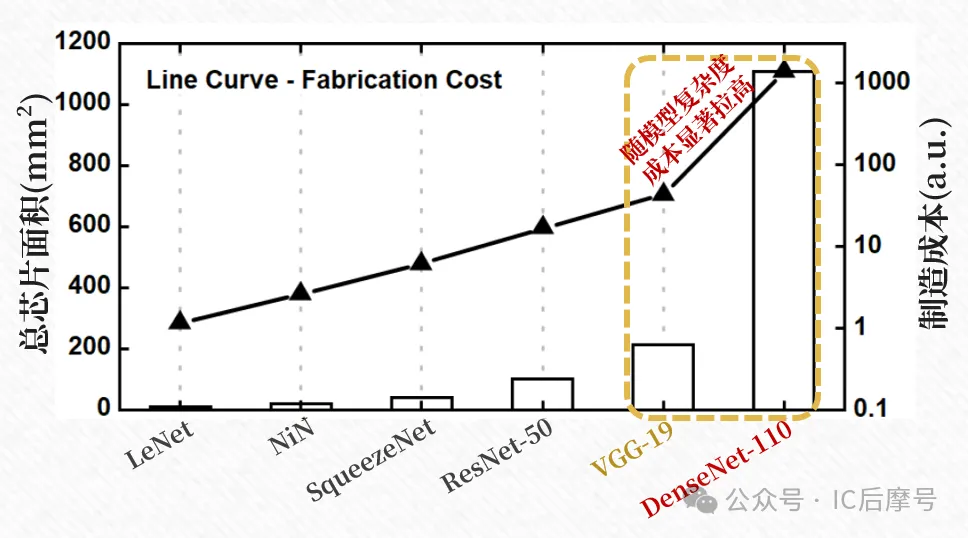

基于交叉开关的存内计算架构显著提高了深度神经网络加速的吞吐量和能效,存内计算架构假设所有DNN权重都存储在一个单一芯片上,以减少片外存储器访问并最大化并行计算。然而,随着深度神经网络模型规模的增大,单片加速器方法会增加芯片面积、制造成本和片上存储。

面积和制造成本的增加归因于更大的深度神经网络规模(权重)和分支结构。因此,解决基于存内计算的深度神经网络加速器制造成本增加的问题可以对AI芯片项目产生巨大效益。

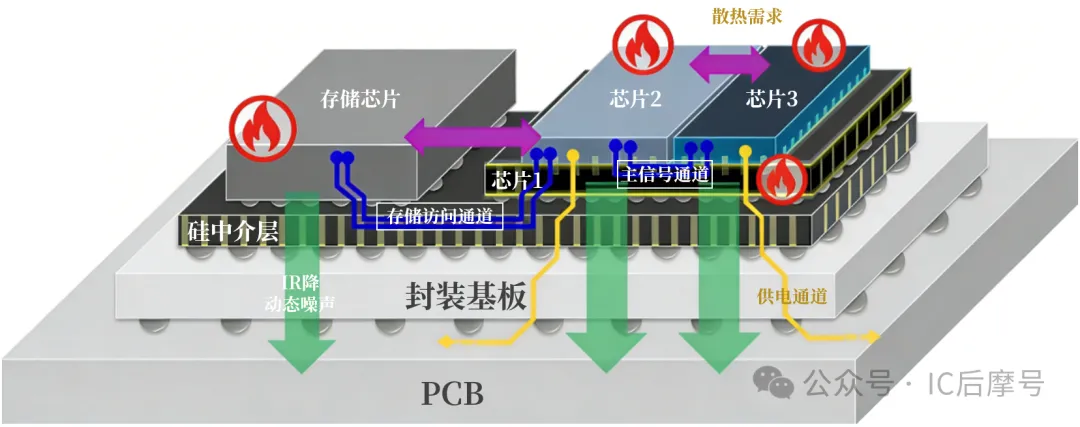

基于芯粒的架构(如上图架构)为单片存内计算架构提供了一种可扩展且有前景的替代方案。多个芯粒使用硅中介层或有机基板集成在一起,形成完整的大规模系统。与单片芯片相比,每个芯粒面积更小,具有更高的制造良率和更低的制造成本。

这里介绍一种芯粒的存内计算架构及其仿真方法(后者以下简称仿真器)将器件、电路、架构、片上网络(NoC)、封装内网络(NoP)和DRAM访问估算集成在单一框架下,用于设计空间探索。

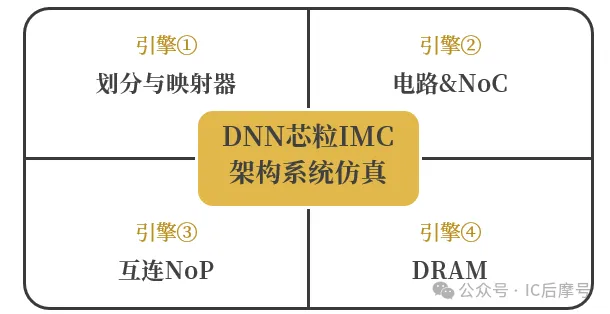

仿真器包括四个主要组件:1)划分与映射引擎、2)电路与片上网络引擎、3)封装内网络引擎和 4)DRAM引擎,利用Python引擎融合,并与流行的深度学习框架(如TensorFlow和PyTorch)连接。

仿真器同时使用基于模型的仿真和周期精确的仿真组件,从而允许对广泛的深度神经网络和数据集进行可扩展且准确的性能评估,其特点:

自身架构灵活

支持多种深度神经网络到存内计算芯粒和交叉开关的划分与映射方案

生成不同类型的基于芯粒的存内计算架构

具有较低的仿真时间

适用于快速的设计空间探索

2. 基于芯粒的存算一体架构

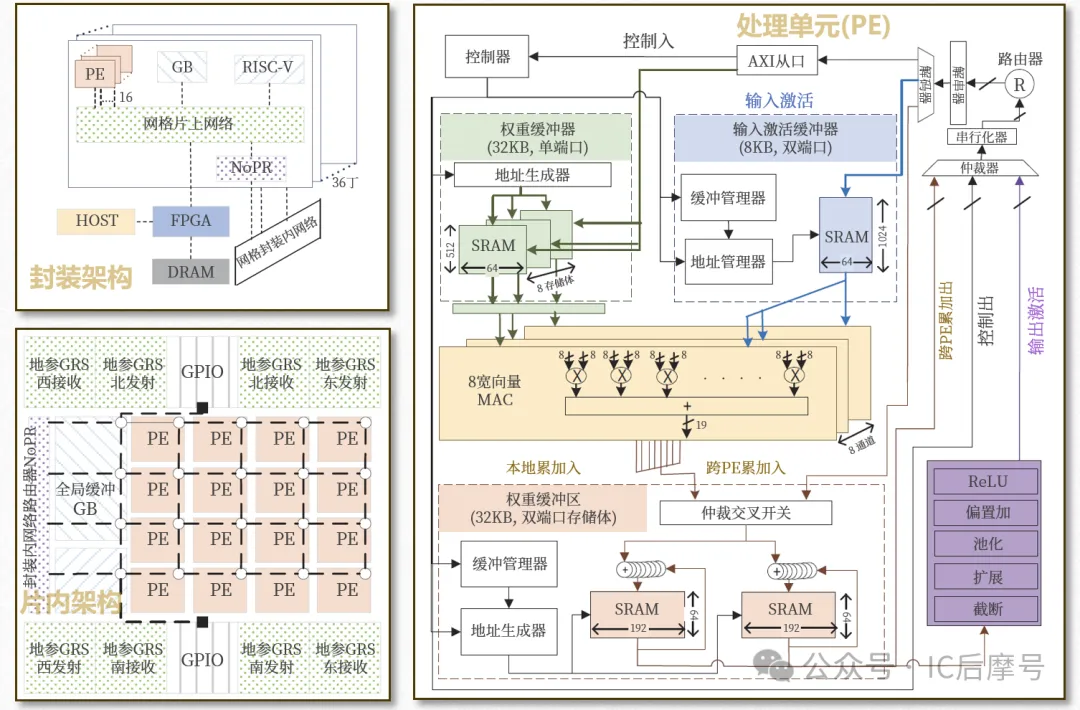

仿真器支持同构芯粒架构的存内计算架构,同时也支持定制芯粒架构。前者要求芯粒的数量是固定的(用户定义),后者则要求存在映射深度神经网络所需的芯粒数量。

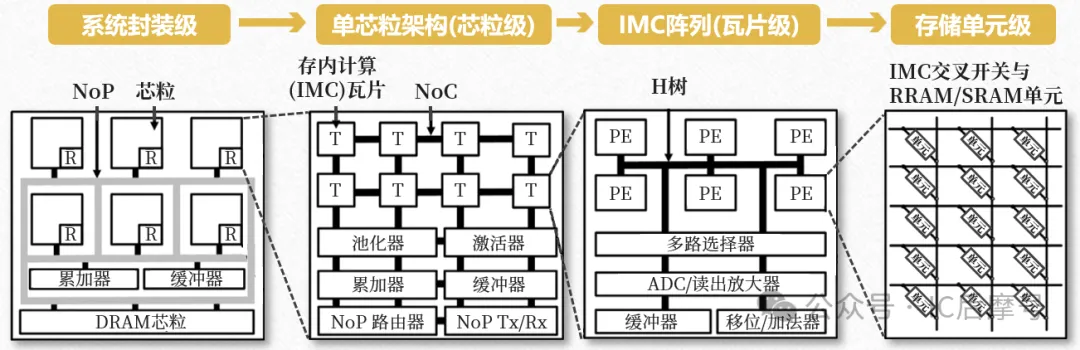

仿真器架构由一组内部包含存内计算单元的芯粒阵列、一个全局累加器、一个全局缓冲器和DRAM组成。仿真器支持基于SRAM和RRAM的存内计算架构。

同构芯粒的跨级计算架构

每个芯粒使用封装内网络(NoP)结构进行连接。全局缓冲器和累加器用于累积跨芯粒的结果,DRAM芯粒用于存储预训练算法的权重,仿真器假设所有权重都存储在片上。

每个存内计算(IMC)芯粒包含一个由片上网络连接的存内计算瓦片阵列。存内计算瓦片由处理单元(PE)阵列或交叉开关阵列组成,这些阵列包含基于RRAM或SRAM的存储单元。

存内计算阵列采用模拟计算来执行乘累加操作(MAC)。存内计算外围的外围电路包括列多路复用器、模数转换器或读出放大器以及移位与加法电路。

列多路复用器允许在多个存内计算列之间共享模数转换器或读出放大器;

模数转换器或读出放大器将模拟值转换到数字域;

然后,根据位重要性,使用移位与加法电路对数字值进行移位和累加;

最后,来自不同存内计算阵列的生成结果使用全局累加器和缓冲器进行累加;

池化单元用于执行最大或平均池化操作,而激活单元实现非线性激活函数。

存内计算芯粒在瓦片级使用片上网络(NoC)来连接其内部的不同单元。在处理单元级,采用点对点互连(如H树)进行片上通信。

芯粒内的每个瓦片利用一个五端口路由器和X-Y路由机制来执行片上的数据移动。片上网络(NoC)的飞字(flit)宽度和工作频率可由用户配置。

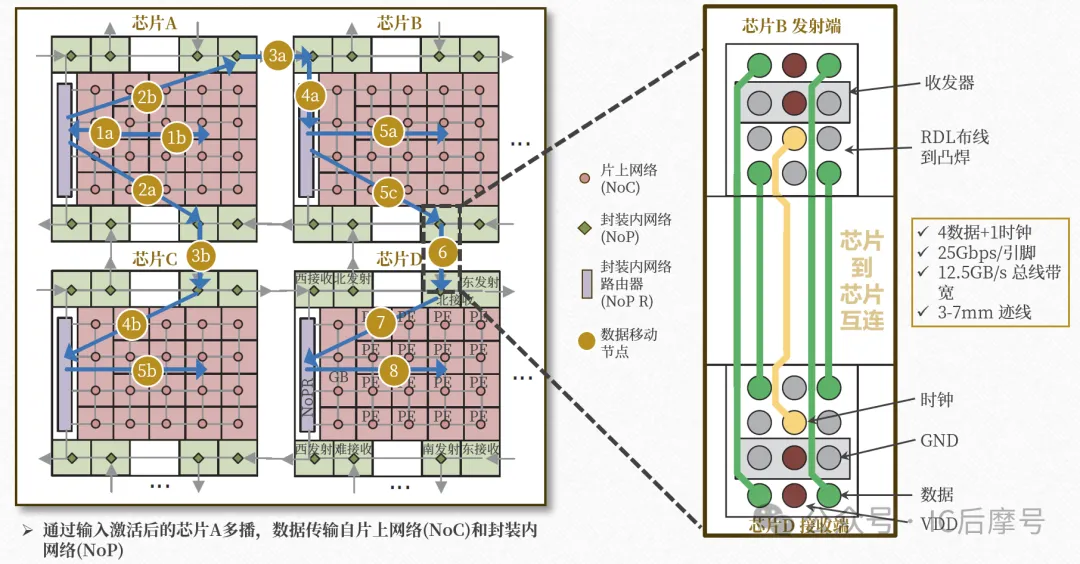

在芯粒级,芯粒阵列使用封装内网络(NoP)结构连接,该结构利用中介层进行布线。此外,仿真器在芯粒级的数据移动中采用无源中介层。

本例中的互连布线配置

每个芯粒包含一个定制的NoP收发器、一个时钟电路(锁相环PLL)和一个路由器。路由器执行数据包调度,并使用专用端口将数据传输到收发器。收发器利用定制的信号传输技术在封装内网络中执行数据传输。

3. 仿真基准测试

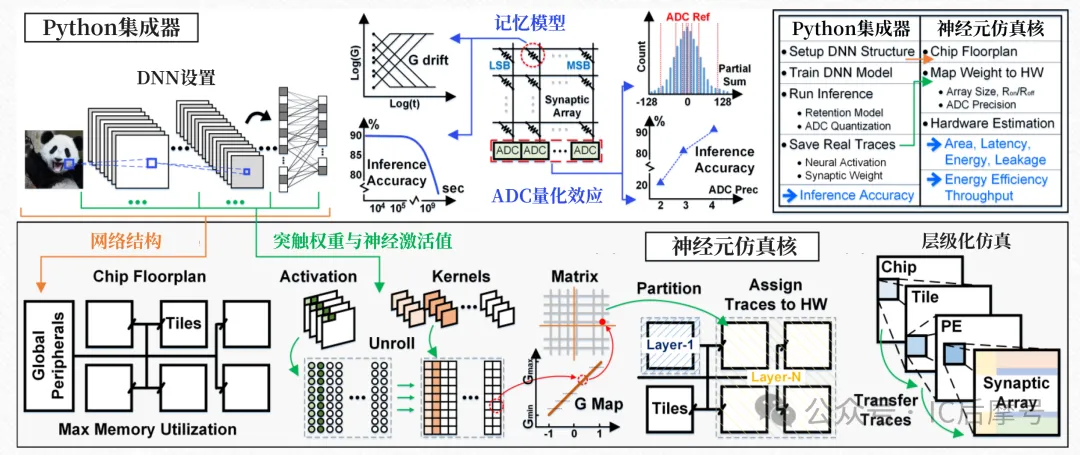

仿真器将器件、电路、架构、片上网络、封装内网络和DRAM集成到一个框架中,用于对基于芯粒的存内计算架构进行系统级分析。

仿真的DNN芯粒存内计算性能基准测试框架

仿真器利用一组用户输入,生成多个硬件性能指标的值,例如面积、延迟、能量、能效、功耗和存内计算交叉开关利用率。

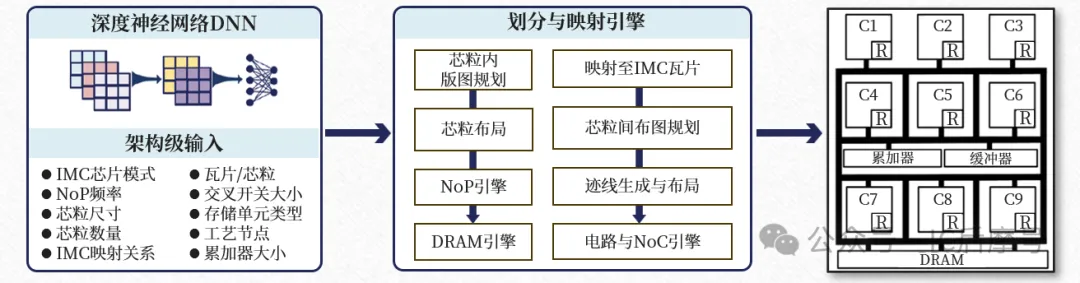

a. 划分与映射引擎

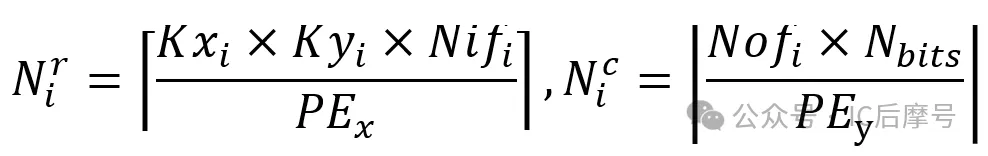

以逐层方式执行深度神经网络到基于芯粒的IMC架构上的划分和映射。对于给定的第i层,令其权重矩阵为Wi,表示为Kxi×Kyi×Nifi×Nofi。Kx和Ky表示卷积核大小,Nif表示输入特征数量,Nof表示输出特征数量,映射方案:

其中Nr和Nc是映射DNN中第i层所需的存内计算交叉开关的行数和列数。PEx和PEy表示存内计算交叉开关阵列的大小,Nbits表示DNN权重的数据精度。Nr和Nc的乘积给出了映射DNN存内计算交叉开关阵列的总数。

划分与映射引擎假设DNN层不能跨多个芯粒划分,并且单个芯粒可以支持多个层以实现高存内计算利用率。

同构架构由固定数量的IMC芯粒组成。这导致小型DNN内计算芯粒的一个子集,而较大的DNN则使用所有可用的IMC芯粒。

定制IMC架构由映射所考虑的DNN所需数量的IMC芯粒组成。在划分和映射之后,仿真器执行芯粒间和芯粒内的布局规划与放置,从而确定整体架构。

b. 电路与NoC引擎

电路与片上网络引擎由一个电路估算器和一个互连估算器组成,它们对基于芯粒的存内计算架构的电路和片上网络组件进行基准测试。

电路估算器评估架构中每个存内计算芯粒、全局累加器和全局缓冲器的性能。该引擎的输入包括:①芯粒间和芯粒内布局、②每层芯粒和存内计算交叉开关数量、③逐层存内计算利用率、④技术节点、⑤工作频率、⑥存内计算单元类型、⑦每单元位数、⑧读出模式(逐行或并行)以及⑨模数转换器精度等。

芯粒内电路包括:存内计算交叉开关阵列及相关外围电路、缓冲器、累加器、激活单元和池化单元。外围电路包括:模数转换器、多路复用器电路、移位与加法电路以及解码器。

一款神经元仿真器结构

通过神经元仿真器(上图)进行电路校正,对性能以逐层方式进行估算。每个芯粒执行深度神经网络中计算的一个子集,并针对每个芯粒进行评估。全局累加器和全局缓冲器中的总累加的评估获得整体硬件性能。

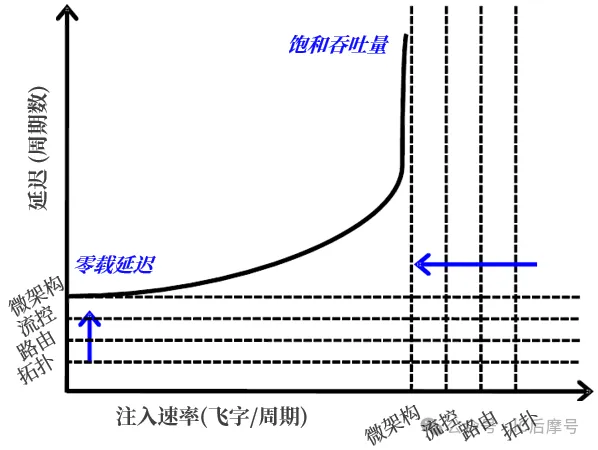

互连估算器。则详细考虑芯粒内多层之间通信的成本。仿真器采用NoC进行芯粒内通信,通过一个定制的周期精确仿真器评估片上网络性能。

延迟-吞吐量曲线:用于测量互连网络性能

仿真器基于每层的输入激活、芯粒数量、层到芯粒映射、量化位精度和总线宽度生成一个跟踪文件。对芯粒内的每一层,确定源瓦片和目标瓦片信息,并计算传输的数据包数量。

利用数据包数量、源瓦片数量和目标瓦片数量,获得一个由源瓦片ID、目标瓦片ID和时间戳组成的元组,利用该元组评估NoC上的芯片内通信。

c. NoP引擎

封装内网络(NoP)引擎评估基于芯粒的存内计算架构中NoP互连的性能。NoP性能评估包含两个主要部分:1) NoP延迟估算,以及 2) NoP面积和功耗估算。

同样采用周期精确的仿真器进行延迟评估。基于划分与映射引擎生成的芯粒间数据量,为NoP个跟踪文件。NoP互连参数进行详细建模,生成RLC参数。利用跟踪文件和RLC参数,周期精确的仿真器评估NoP互连的延迟。

NoP由发送器和接收器电路、锁相环时钟电路、NoP路由器以及封装内布线组成。封装内布线和路由器的面积与能量成本由周期精确的仿真器评估。仿真器利用每比特能量、总线宽度、电路面积成本、传输比特数以及发送器/接收器对数来生成NoP的总面积和能量成本。

d. DRAM引擎

基于芯粒的IMC架构包含一个构成外部存储器的DRAM芯粒。DRAM引擎在推理操作之前执行一次深度神经网络权重的传输。因此,对于给定的深度神经网络,DRAM成本保持不变。

该引擎使用DRAM请求生成器RAMULATOR(Y. Kim, 2015)进行延迟评估,使用VAMPIRE(S.Ghose, 2018)仿真器进行功耗估算(支持基于DDR3和DDR4的DRAM选项)。

根据深度神经网络规模,仿真器首先生成一组跟踪信息或请求,以将权重传输到IMC架构。仿真器利用DRAM请求来评估将权重传输到存内计算芯粒的延迟,最后得到的延迟和DRAM请求,再通过功耗评估工具生成功耗。

4. 仿真结果与小结

3.1 实验设置

基于芯粒的IMC性能仿真按照下表配置。

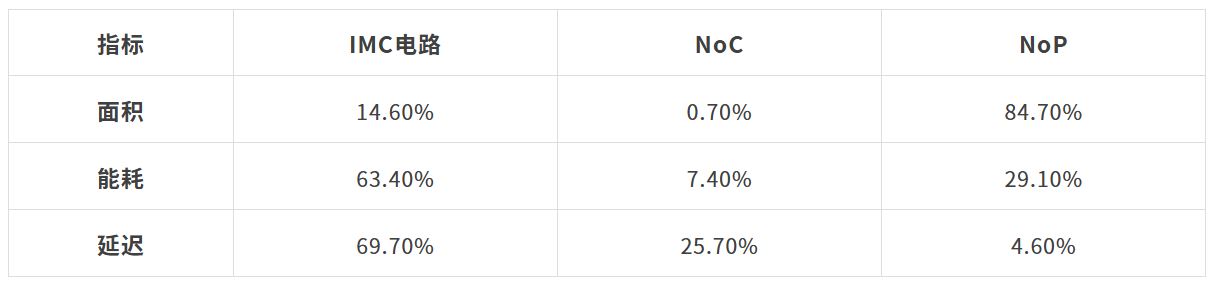

对定制型基于芯粒的RRAM IMC架构的总面积、能量和延迟指标的分解情况如下表。在CIFAR-10数据集上实现ResNet-110上实现,指标被分解为IMC电路、NoC片上网络和NoP封装内网络。

IMC电路包括存内计算交叉开关阵列及外围电路、缓冲器、累加器、池化单元和激活单元;

NoP组件包括NoP互连、NoP路由器以及NoP驱动器和时钟电路;

NoC主要是互连和路由器。

面积方面。NoP以84.7%的比例主导了总面积,而片上网络贡献最小。采用差分信号的NoP驱动器为32个通道带来了额外的电路。NoP路由器的面积由技术节点和端口数量决定,而NoP链路的面积取决于布线参数。

能量和延迟方面。IMC电路组件占据主导地位,贡献率分别为63.4%和69.7%。NoP在能量方面贡献第二高,而NoC在延迟方面贡献第二高。

总体而言,面积主要由封装内网络决定,而能量和延迟主要由存内计算电路决定。

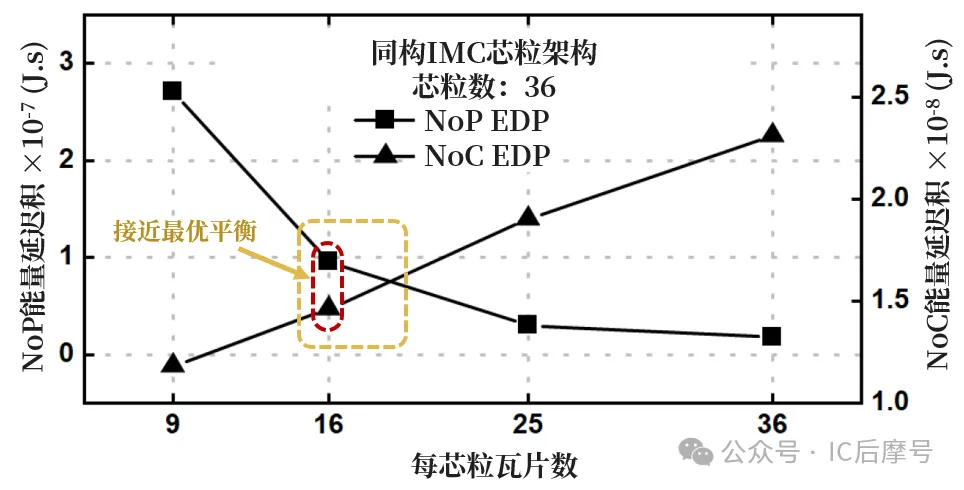

NoP和NoC的比较。对比同构芯粒存内计算架构在36个芯粒计数配置下的NoP和NoC的能量延迟积(EDP)。

36个芯粒计数配置的同构RRAM基芯粒存内计算架构的NoP和NoC积显示:随着每个芯粒的瓦片数量增加,NoP的能量延迟积降低。NoP的降低是由于计算局部化导致芯粒间通信量减少。同时,NoC能量延迟积随着每个芯粒瓦片数量的增加而增加,这是因为片上网络规模变大。

在该数据集和模型中的权衡为:每个芯粒16个瓦片在片上网络和封装内网络成本之间提供了接近最优的平衡。

仿真时间。配备12核CPU和32GB RAM的Intel Xeon W2133平台上运行仿真:从几分钟到几小时不等,具体取决于深度神经网络的大小。总仿真时间包括划分与映射、IMC电路与NoC仿真、NoP估算和DRAM访问估算。对于以上所述数据集和模型仿真估算12分钟,对于ImageNet数据集上具有1.38亿参数的VGG-16,则需要4.26小时。

参考文献

Gokul Krishnan, Sumit K. Mandal, System-Level Benchmarking of Chiplet-based IMC Architectures for Deep Neural Network Acceleration, 2021

Brian Zimmer, A 0.11 pJ/Op, 0.32-128 TOPS, Scalable Multi-Chip-Module-based Deep Neural Network Accelerator with Ground-Reference Signaling in 16nm, 2019