作者:赵瑜斌Robin,来源:IC后摩号

先进处理器(CPU、GPU等)遭遇利用率墙时,开发重心从制造工艺转向工艺感知型计算机架构,聚焦能效。

流语义寄存器(Stream Semantic Registers, SSR):轻量、非侵入式的 RISC‑V 指令集扩展,将内存访问隐式编码为寄存器读写,大幅消除加载 / 存储指令。

Content

1 概述

2 架构

核心架构

数据移除器

中断与异常

存储系统

3 编程模式

4 性能分析

ISA级影响

核函数

5 设计与实现结果

单/多核对比

阿姆达尔定律与强扩展性

自动编码生成

处理器对比

6 相关研究与小结

流式加速器、环加速器、数据地址生成器、向量处理器

小结

在一款现有多核簇的 RTL 中实现该扩展,基于22nm工艺完成综合。该扩展在各类核函数上带来2~5倍的架构级加速,核心面积仅增加 11%。

单核心顺序代码速度提升3倍,多核簇达到相同性能所需核心数减少至 1/3。计算单元利用率接近100%,使多核簇能效提升2倍。

SSR可将指令取指量最高降低 3.5 倍,指令缓存功耗最高降低 5.6 倍。编译器可自动将嵌套循环映射至 SSR,对程序员完全透明。

1. 概述

基于"加载-存储"范式构建的顺序处理器内核,在保持功能单元忙碌方面面临能效挑战。假设我们要对一个长浮点(FP)向量计算点积。

flw ft0, 4(a0!)flw ft1, 4(a1!)fmadd.s ft2, ft0, ft1, ft2

从内存中加载两个数值(flw),然后相乘并累加结果(fmadd.s)。假设迭代与指针调整通过硬件循环和加载后自增完成,都是成本很低的微架构增强。

在单发射内核中,执行上述操作至少需要 3 个周期。每 3 条指令中只有1条执行实际计算,FPU利用率最多只有 33%。根本问题:在“加载-存储”架构中,内存数据的传入与传出被编码为显式指令。如果机器每周期只能发射一条指令,那么每一次加载和存储都会在FPU中引入至少一个空闲周期。内核的运算强度越低,该问题就越突出。

让处理器的功能单元尽可能保持忙碌有多重原因:1)近阈值工作区间,或高性能计算(HPC)、数据中心的工作温度下:漏电流是功耗的重要组成部分,增加单次计算能耗,降低整体能效;2)面积受限场景(如嵌入式应用)中:空闲周期会带来高昂的性能代价。

实现高 FPU/ALU 利用率是微架构设计的终极目标。SSR核心思想:对于具有规则数据访问的指令序列,允许将加载 / 存储编码到任意指令中,而非使用显式加载 / 存储指令。

通过为少量寄存器赋予流语义来实现这一点:对该寄存器的读或写操作会分别触发向内存系统的读或写。置于处理器内核之外的地址生成单元(AGU),允许这些内存访问遵循可编程的仿射地址模式,这类模式在数字信号处理(DSP)、模板计算、机器学习等诸多计算密集型负载中极为常见。

遵循这种可预测地址模式的一个关键优势是:数据可以被主动加载,相当于实现了一种预取。上例被改写为(其中 ft0 和 ft1 现在具有流语义):

fmadd.s ft2, ft0, ft1, ft2

直观上预期的加速比为3倍(上限×3.7)。RISC架构的寄存器文件扩展,支持在任意指令中隐式编码数据传输。在多核平台上所需的架构改动。

架构

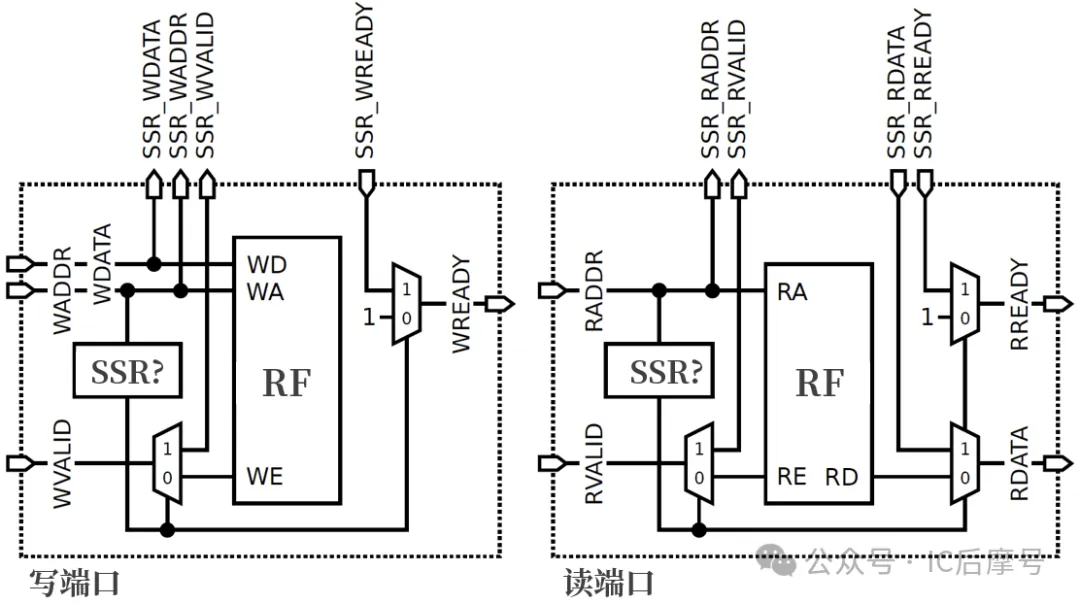

架构更改所隐含的高级数据路径。不直接将读写访问路由到寄存器文件,而是首先确定被访问的寄存器是否启用了流语义,如果是,则将访问重新路由到相应的流接口。寄存器文件的每个端口都有一个对应的流接口。具有“IFD”扩展的RISC-V分配了32个整数寄存器和32个浮点寄存器,并使用5位地址来寻址它们。

核心架构。实现中使用的RISC内核将这些融合到一个具有64个寄存器和6位地址的寄存器文件中,其中最高有效地址位根据请求指令是整数操作还是浮点操作来设置。

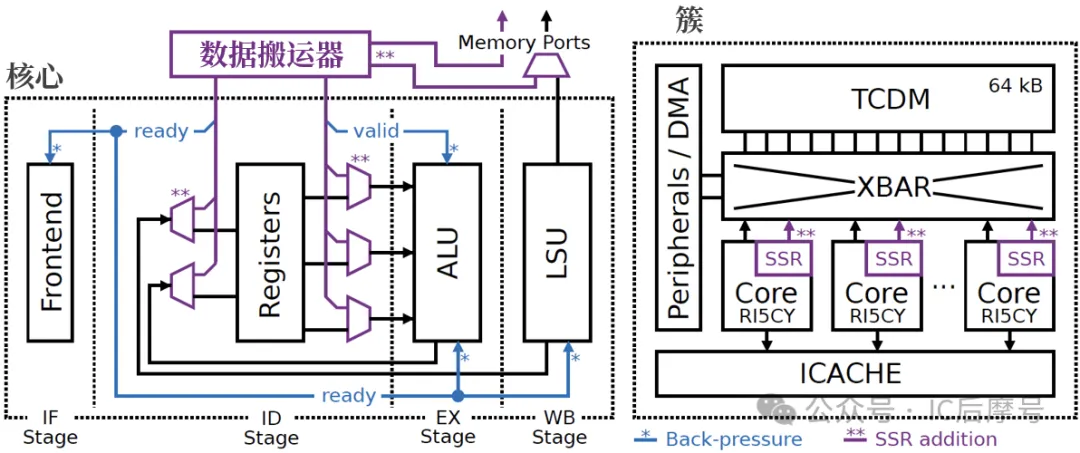

左图:单核中SSR扩展的高级数据流。对某些寄存器的读写访问被过滤并转移到处理器核心之外。其后,数据搬运器为这些访问分配内存地址,并将其转发到内存系统中。

右侧:多个核心的集群,通过日志互连(XBAR)连接到TCDM和外围设备。蓝色*:用于控制背压的流水线添加项;紫色**:SSR数据路径添加项。

每个寄存器文件写端口(左)和读端口(右)都需要额外的电路来支持流语义。这些附加电路作为核心现有寄存器文件(RF)的封装实现。SSR访问检查“SSR?”等同于计算A∈{t0, t1, ft0, ft1} & E,其中A是寄存器地址,E是SSR使能的CSR位。

流水线考量。由于其新获得的流特性,寄存器文件失去了幂等性。比如,一条多周期指令可能在其执行的所有周期(除了最后一个周期)向其目标寄存器应用虚假数据,并且仅在其最后一个周期呈现有效数据。

作为优化,处理器可以选择在所有周期启用寄存器写入,知道最后一个周期最终会用有效结果覆盖虚假数据。类似地,一条指令即使在流水线停顿期间也可能持续读取寄存器。使用SSR时,这种优化是不可能的,必须添加额外的信号以确保每条指令恰好访问其寄存器一次。

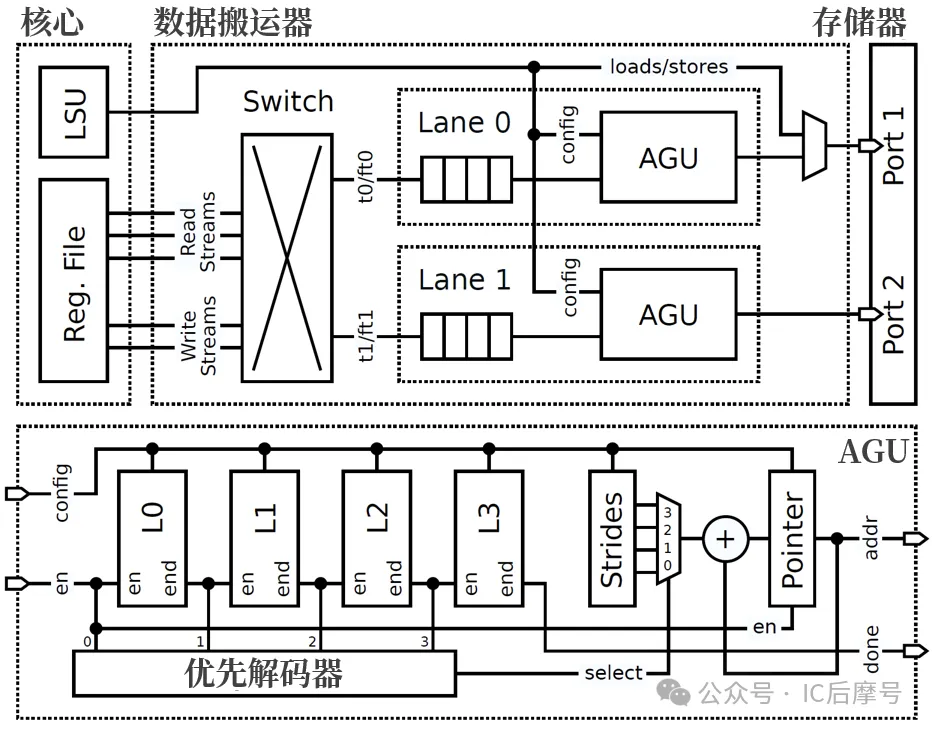

数据搬运器。寄存器文件的每个端口在内核边界处都作为一个独立的流暴露出来(三读流和两写流)。一个开关使用寄存器地址将这些流上的每次访问映射到目标数据移动器通道。包含两个这样的通道,一个用于 `t0/ft0`,一个用于 `t1/ft1` 寄存器。

数据搬运器:将寄存器访问流转换为相应的内存地址和访问。

单个AGU:包含四个嵌套循环,“L0”至“L3”为循环计数器,模式通过“config”接口配置,该接口可修改循环计数器、步长和指针寄存器。

中断和异常。AGU和SSR的启用状态为处理器内核添加了额外的隐式状态,必须妥善保存/恢复,识别和处理异常:无异常、延迟异常、精确异常。

存储系统。SSR扩展会提升内核可向存储系统请求的峰值内存带宽,需合理设计流、数据搬运器与内存端口数量。内存流量上限由寄存器文件端口数、指令操作数、数据搬运器数量共同决定;采用LSU 与数据搬运器复用同一内存端口的低成本设计,兼顾带宽与面积开销。核函数运算强度匹配端口数,如2个端口即可支撑乘累加等高频算子满负荷运行。

编程模式

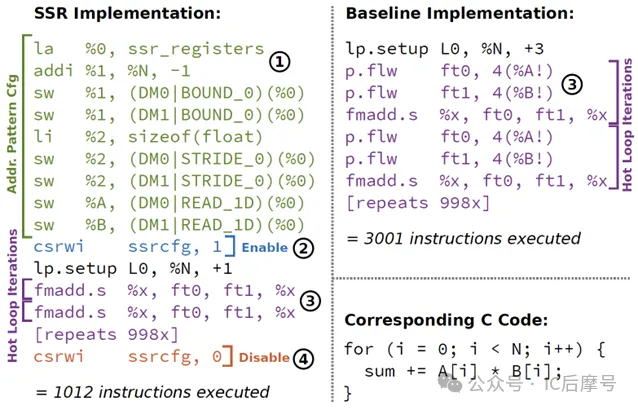

SSR 使用流程固定为:配置地址模式 → 启用流语义 → 执行计算循环 → 关闭流语义:

数据搬运器通过内存映射寄存器配置,支持最多 4 层嵌套仿射地址循环,软件只需发出对应数量的计算指令。

编译器可在 LLVM 中自动将满足条件的循环映射到 SSR,对程序员透明,无需手写汇编。

短循环因配置开销可能不划算,需按迭代次数选择性启用SSR。

静态单线程寄存器(SSRs)基本使用模式

通过向内存映射地址生成器寄存器写入数据来配置地址模式(1)

通过向ssrcfg CSR写入数据来启用流语义(2)

执行实际的热循环(3)

并再次禁用流语义(4)

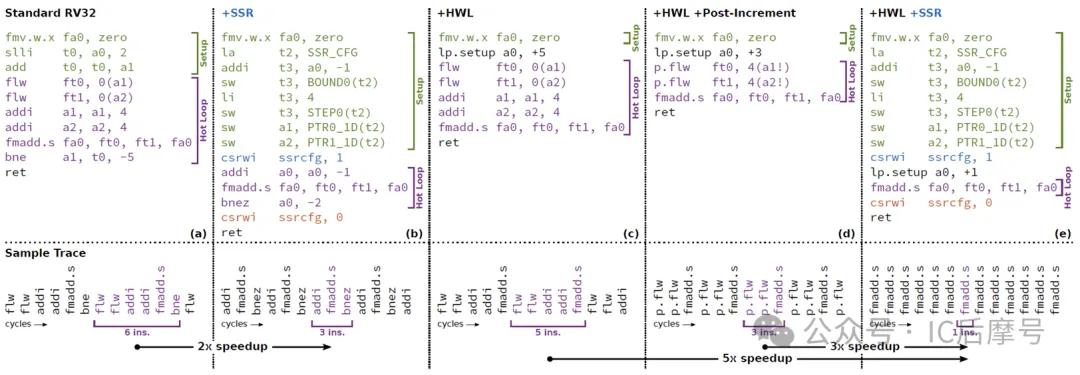

带有RI5CY自定义扩展的基线RISC-V实现,与静态单线程寄存器(SSRs)的情况不同,每个热循环迭代中多了两次额外的后增量加载操作。

性能分析

ISA架构。SSR在标准RISC-V基础上可实现2~5 倍架构加速,将 FPU/ALU 的计算利用率从约33%提升至接近100%,并能有效摊销配置开销、规避数据依赖停顿。

不同ISA扩展的汇编内核对比与每个内核的示例执行轨迹

(a)基线RV32处理器

(b)带单步寄存器(Single-Step Register,SSR)扩展的RV32;

(c)带硬件循环(Hardware Loops,HWL)的RV32;

(d)带硬件循环和后增量加载(post-increment loads)的RV32;

(e)带硬件循环和单步寄存器扩展的RV32。

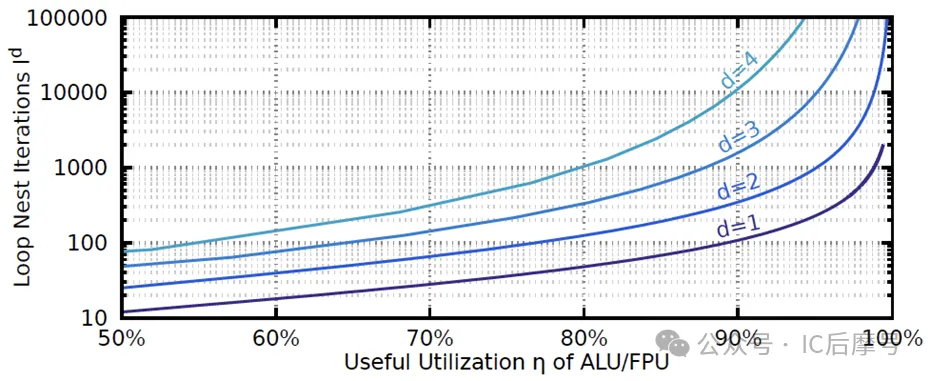

摊销配置提升利用率

使用带单边长(边长为1)的降维超立方体(ad-dimensional hypercube)的带SSRs(单边长超立方体)的有用ALU/FPU利用率,总迭代次数为1d。

循环嵌套越深,总体循环配置开销越大,需要运行更长时间的循环才能达到与低维循环相同的有用利用率。

核函数。SSR 对归约、模板计算、GEMM、FFT 等典型算法均取得稳定收益,速度提升达到2.0~3.7 倍,让执行瓶颈从指令取指转移到内存数据接口,实现更高效的数据供给与计算匹配。

设计与实现结果

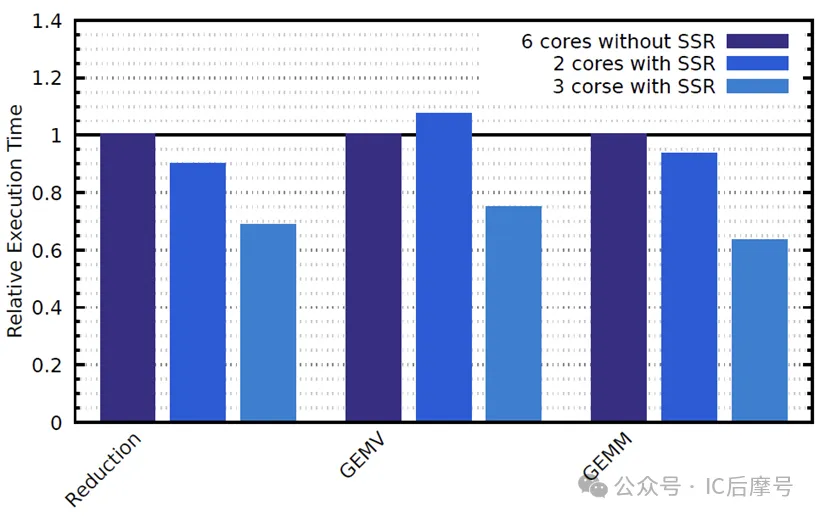

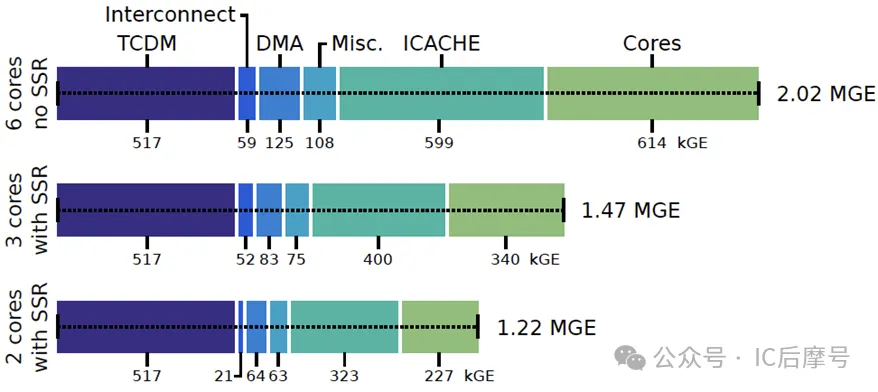

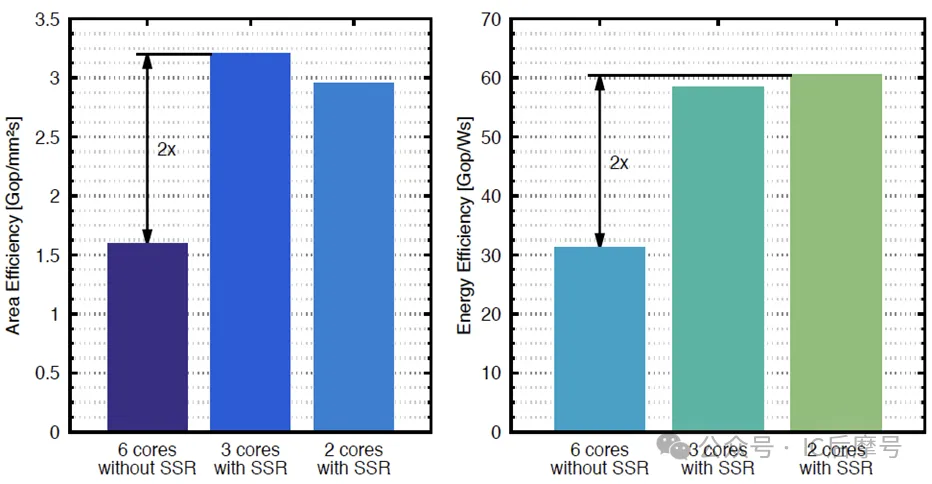

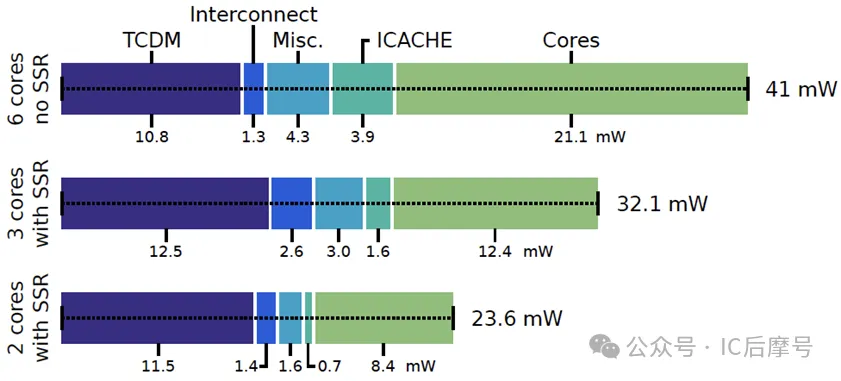

多核对比。SSR 可让集群核心数减少 2~3 倍仍保持同等性能,面积与能耗同步大幅下降,面积效率与能效均提升约 2 倍;同时指令取指减少 3~3.5 倍,指令缓存功耗降低 5.6 倍。

执行时间分别相比:无SSRs的6核3FPU核、有SSRs的3核3FPU核、有SSRs的2核2FPU核

三组核的面积细分

三种簇配置的面积效率和能源效率比较

以簇在每单位面积和功耗下,在减少工作量时每秒实现的运算次数

三个簇的功耗分解

阿姆达尔定律与强扩展。SSR 直接加速串行代码,提升单线程资源利用率,大幅降低达到目标性能所需的核心数量,显著缓解并行同步、分片带来的串行开销,改善强扩展效果。

自动代码生成。基于 LLVM 可实现循环到 SSR 的自动映射,性能接近手动优化,对程序员透明,现有程序只需重新编译即可受益,仅需优化配置阶段指令选择即可进一步提升收益。

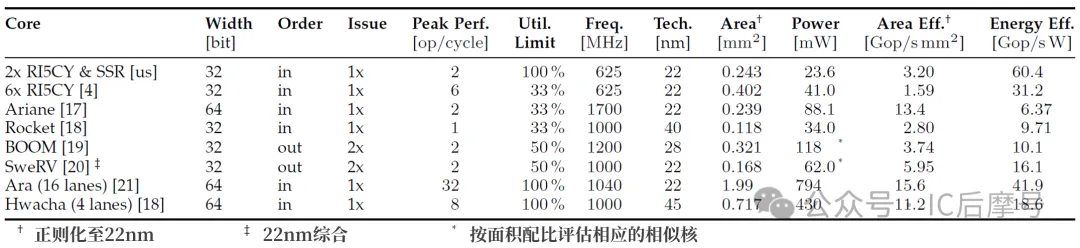

商用处理器对比。SSR提供一种更轻量的提升FPU利用率的方案,直接解决冯・诺依曼瓶颈的同时,也可用于超标量处理器,作为SIMD并行化的替代或补充方案。SSR方案在能效上大幅领先通用CPU核,与高端GPU相当,且无需 SIMD/SIMT 向量化与复杂数据重排,编程更简单、硬件更轻量。

峰值利用率。表中将每个内核理论上可达到的最大利用率(“Util. Limit”)定义为问题规模 N 趋于无穷时的利用率极限。比如,无 SSR 的 RI5CY 上点积的固定配置开销为 2,循环体为 3 条指令。有 SSR 时开销为 7,循环体为 1 条指令。每次循环迭代包含一次 “有效” 操作。因此利用率极限为:

无 SSR:lim (N→∞) N/(2+3N) = 33%

有 SSR:lim (N→∞) N/(7+N) = 100%

相关研究与小结

流加速类工作:SSR 借鉴了 NTX 协处理器、乱序处理器流访问、WM 机器的思路,但以更轻量的方式把流语义直接嵌入 RISC‑V 内核寄存器,无需显式卸载指令或专用接口,对单发射顺序核收益更突出。

循环加速类工作:同类方案多面向大型超标量处理器优化前端开销,而 SSR 可彻底消除加载 / 存储指令,支持嵌套循环,在小面积低功耗核上效果更显著。

数据地址生成器(AGU):传统 DSP 与超标量处理器的 AGU 功能强但面积功耗高、需要专用指令;SSR 用极简仿射 AGU 即可实现 2~3 倍加速,且不增加 ISA 复杂度,通用性更强。

向量处理器:RISC‑V 向量扩展(如 Ara、Hwacha)与 ORCA LVE 虽能达到 100% 利用率,但需要大量 shuffle、散射 / 聚集操作与严格数据排布;SSR 相当于提供 “免费重排”,编程更简单、硬件更轻量,适用场景更灵活。

在高度DSP优化的RISC-V内核RI5CY中实现SSR扩展。在该场景下,它在各类数据无关核函数上提供 2 倍至 3.7 倍加速,以及 1.5 倍至 2.3 倍能效收益。硬件代价适中,真实核函数上,SSR 将指令取指量减少 3.5 倍,指令缓存功耗降低 5.6 倍。

参考文献

Fabian Schuiki, Stream Semantic Registers: A Lightweight RISC-V ISA Extension Achieving Full Compute Utilization in Single-Issue Cores, 2020