作者:Chen Shaoyi,AMD工程师;来源:AMD开发者社区

在高速数字系统设计中,信号完整性(SI, Signal Integrity)分析是确保系统可靠性的关键步骤。HyperLynx 作为主流 SI/PI 仿真工具,能够方便地对来自 Allegro 的 PCB 设计进行建模与仿真。本文将详细介绍如何将 Allegro 的 PCB 文件导入 HyperLynx,并以差分信号为例,完成从建模到仿真的完整流程。

1. 将 Allegro PCB 工程导入 HyperLynx

HyperLynx 支持多种方式导入 PCB 设计,常用方法包括:

方法 1:直接导入 Allegro .brd 文件

HyperLynx 自带 PCB 转换工具,可直接识别 Allegro 的 .brd 格式文件。

选择对应文件后,软件将自动完成格式转换。

方法 2:导入 ODB++ 文件

如果在 CAD 工具中将 PCB 导出为 ODB++ 文件(.tgz 或 .zip),

HyperLynx 也可以直接打开 ODB 工程进行解析。

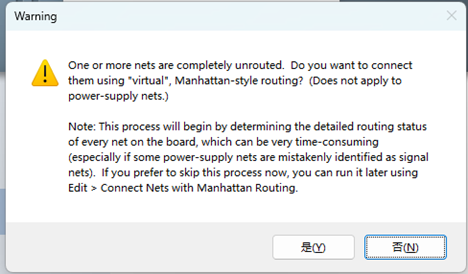

导入完成后,软件通常会提示是否自动布线,一般选择 否,以保持原始布线拓扑。

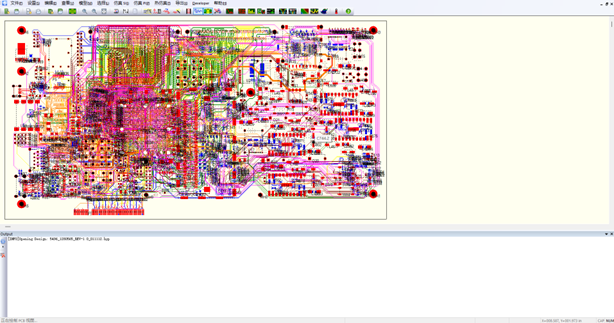

打开后的PCB工程如如所示。

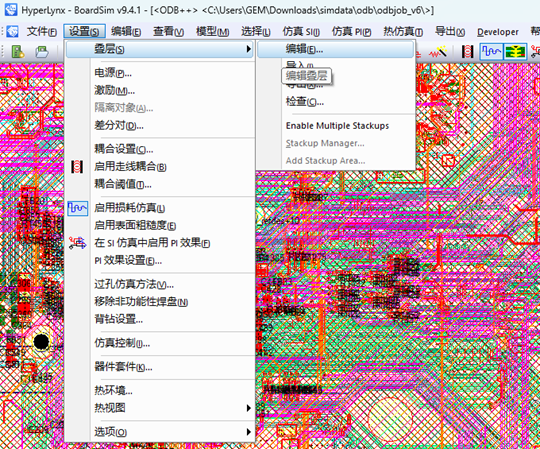

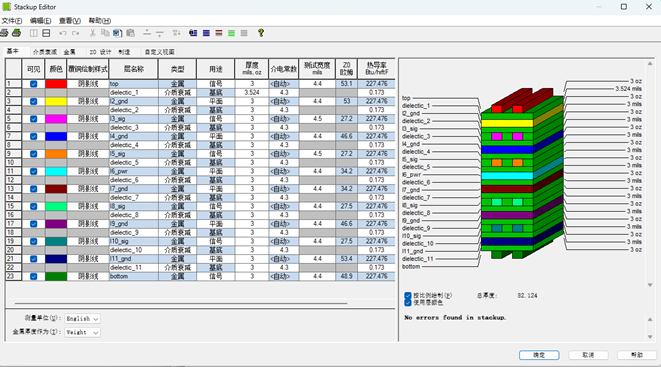

2. 设置 PCB 层叠(Stackup)

为了确保仿真精度,必须根据真实的 PCB 制造信息填写层叠信息。

进入 Stackup Editor 后,设置介质厚度、铜厚、介电常数等参数。正确的层叠对传输线阻抗、传播延迟、耦合系数等均有直接影响。

层叠设置的界面如下图所示。

3. 差分信号仿真流程示例

以下以差分对为例展示典型的仿真流程。

3.1 筛选需要仿真的差分对

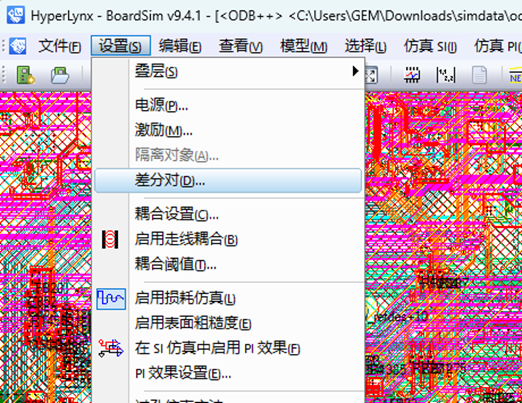

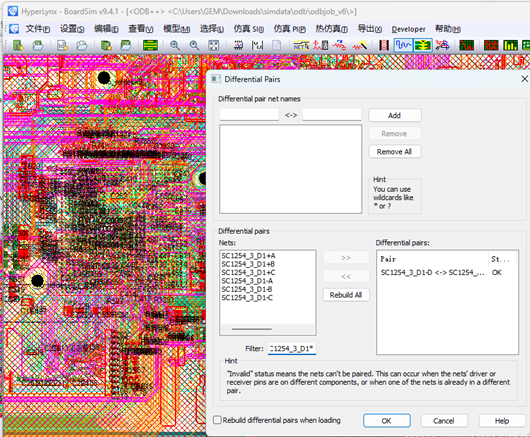

在 HyperLynx 中使用 Filter 功能可以快速筛选出需要分析的差分对。如果 PCB 已经绑定了 IBIS 模型,软件也可根据 IBIS 自动识别差分对信息。

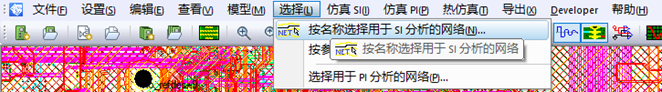

3.2 选择线路用于信号完整性分析

在信号选择窗口中,选中目标差分对并确认,即可进入拓扑提取阶段。

你可以选择:

直接进行板级仿真

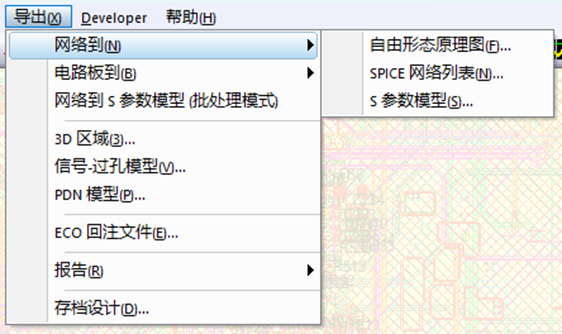

或将提取的网络导入 schematic(原理图)中做结构化仿真

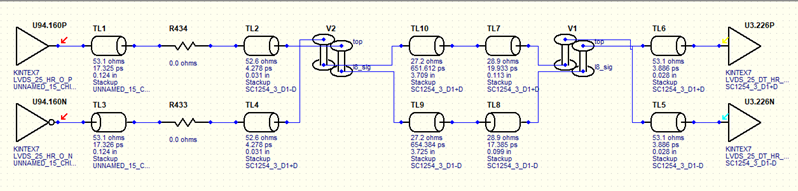

4. 构建仿真拓扑

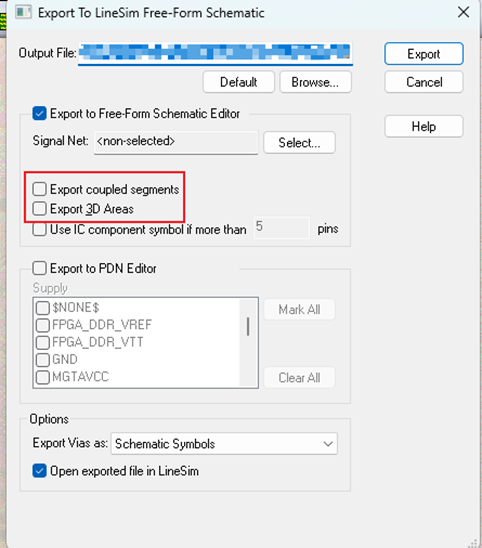

在导入拓扑前,可取消勾选不需要的建模选项,使拓扑简化便于分析。

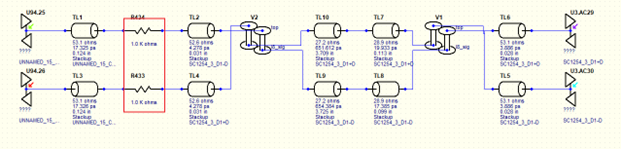

导入 schematic 后,需要检查拓扑结构是否存在问题,例如:

不必要的电阻需替换为 0Ω

未建模的器件需确认处理方式

IBIS 模型路径需正确设置

5. 添加器件模型并绑定 IBIS

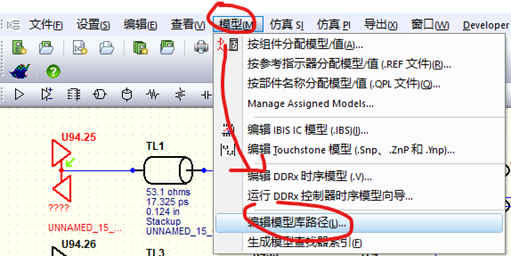

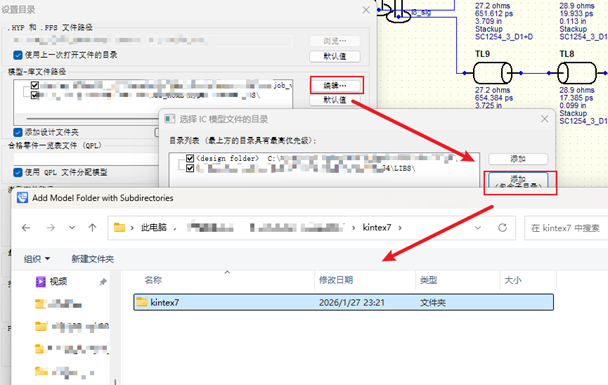

进入模型库设置界面,添加所有需要用到的 IBIS 模型路径。

在没有找到某器件模型的情况下,可以使用功能类似或输出特性接近的 IBIS 模型代替。

例如文中案例中,ADC 的 IBIS 模型缺失,使用了 FPGA 的输出模型代替,以继续完成仿真。

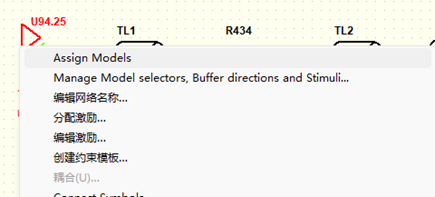

右键点击 schematic 中的器件,选择 Assign Model(赋模型),即可绑定相应 IBIS。

赋值后的模型如图所示。

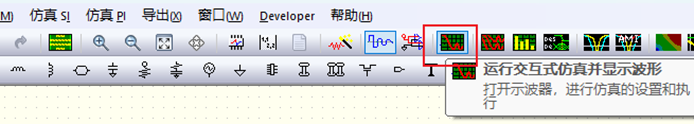

6. 开始信号完整性仿真

模型配置完成后即可执行仿真。

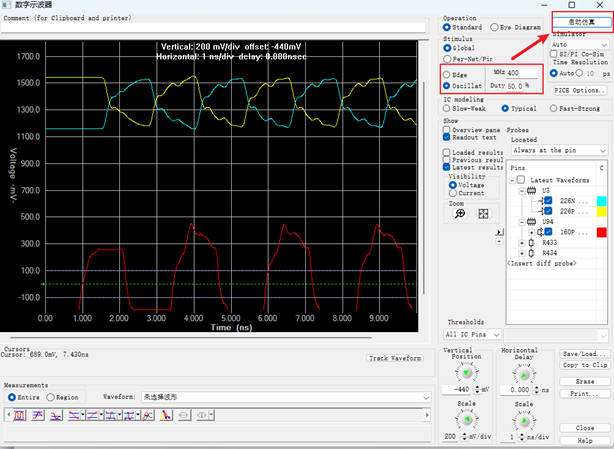

HyperLynx 会生成关键波形,如:

上升沿/下降沿过冲与下冲

眼图(Eye Diagram)

时序裕量

差分模值与共模噪声

通过对比仿真结果,可以判断布线是否满足信号完整性要求,并根据需要优化 PCB 设计。

Probe可以设置位于Package上或者位于Die上。

总结

本文介绍了从 Allegro PCB 文件到 HyperLynx 仿真的完整建模流程。