作者: 来源:根究FPGA

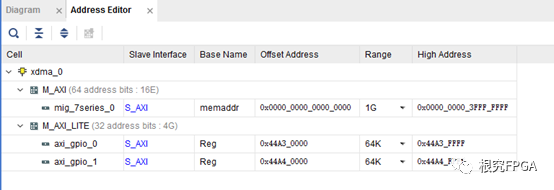

在ZYNQ的地址分配中,可以将每一个Slave接口定义为一个存储器映射,其由一个或多个地址块(目前只遇到过一个地址块),存储区和子空间映射元素组成,可以通过从属接口访问存储器映射(典型的比如DMA应用)。

Address Space地址空间之后定义为存储器的逻辑可寻址空间,可以为Master总线访问的每个从设备进行分组,进行地址分配时默认根据主机进行分组,根据主机是否有对应的连接到从机,从而决定从机是否在这个分组。

以PCIe上位机访问映射到BAR空间的GPIO为例,在进行地址分配时分别为其分配64K的地址空间:

关于地址分配的范围,在ug585的第四章第一节有讲:

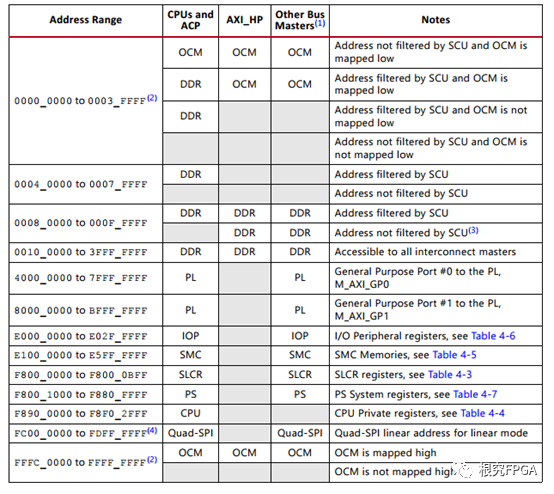

从上图可以看到:总的地址分配空间为4G(2^32个地址空间,每个地址对应8bit的映射空间)。

从0地址开始的1G地址为DDR与256KB的OCM空间,在学习米联客的资料时,总是疑惑为什么在使用PS侧的DDR时要避开前1M的地址空间,当前的理解是该部分地址空间被PS侧的OCM(Onchip Memory)所使用,当用户对这部分这部分空间进行读写访问时,可能造成PS侧运行异常。

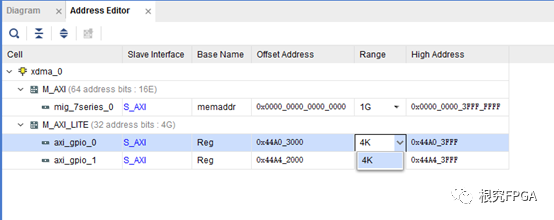

最后说明在对从设备进行地址分配时,每个从设备的地址最小对齐边界为4K,即地址的低12位全为0,这样表示地址范围大小为2^12=4K,4K对齐最大原因是系统中定义一个page大小是4K。所以,为了更好的设定每个slave的访问attribue,就给一个slave划分4K空间:

AXI 协议支持地址非对齐的传输,允许突发传输的首字节地址,即起始地址与突发传输位宽不对齐。举个例子,总线位宽为 32bit 时,如果起始地址为 0x1002 ,则产生了非对齐现象。与 32bit 位宽总线对齐的地址需要能被 4 整除,即 ADDR[1:0] = 2'b0。

对于非对齐写传输,主机会进行两项操作:

(1)、即使起始地址非对齐,也保证所有传输是对齐的

(2)、在首个 transfer 中增加填充数据,将首次传输填充至对齐,填充数据使用WSTRB 信号标记为无效

(此处需要说明TKEEP和TSTRB了,在写传输中,对于填充数据字节,TKEEP对应的位1,对应的WSTRB为0,表示该字节数据无效,仅用于数据填充,实现地址对齐)。