概要

ZYNQ UltraScale+ MPSoC支持支持USB3.0,其功能通过PS侧GTR接口实现。实际设计中,有时希望仅支持USB2.0即可。这里,概要描述仅需要USB2.0场景下的软硬件设计及调试过程。我们在实际设计中,采用了与ZCU102相同的USB PHY芯片(Microchip/USB3320)。

硬件设计

设计中,首先需要保证PHY器件处于正常工作状态,这里要根据PHY器件的器件手册,进行确认,例如:PHY器件的BIAS电压,Regulator输出电压等是否正常,控制器和PHY器件之间的ULPI接口时钟(60MHz)是否正常;其次,利用驱动程序,对PHY器件的寄存器进行操作,例如,针对USB3320,可以通过读PHY器件的Vendor ID或者读写PHY器件的测试寄存器进行验证。

软件设计

Block Diagram

根据实际设计,仅需要对USB2.0的相关IO进行勾选即可,不需要勾选USB3.0接口。

驱动设计

驱动设计参考链接:

1、https://xilinx-wiki.atlassian.net/wiki/spaces/A/pages/18842047/Zynq+Ultr...

2、https://xilinx-wiki.atlassian.net/wiki/spaces/A/pages/18842468/ZynqMp+US...

我在设计实现中,Vivado/SDK版本为2017.4。Xilinx官网给出的AR# 69533指出在2016.4、2017.1、2017.2版本中,由于PIPE3 clock在没有USB3.0的情况下被禁用,会导致USB接口不工作。在2017.4中确实没有碰到该问题,如果使用上述版本碰到该问题,请参考AR#69533进行解决。

参考链接:

https://www.xilinx.com/support/answers/69533.html

Xilinx给出的example路径为:

SDK\2017.4\data\embeddedsw\XilinxProcessorIPLib\drivers\usbpsu_v1_3\examples

测试验证

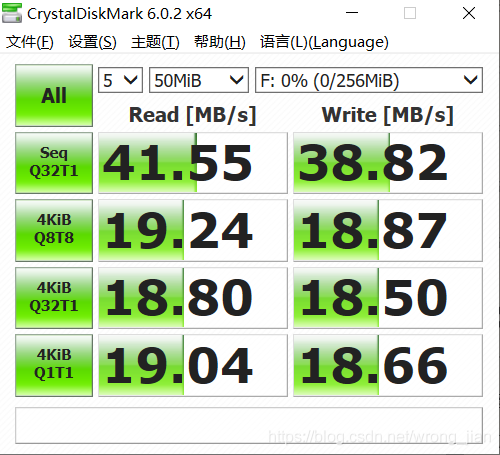

可以使用Xilinx WiKi推荐的CrystalDiskMark进行测试:

总结

驱动设计调试是软硬件结合的设计调试,作为基础,硬件上首先要从设计到调试保证正常;其次,尽量利用好已有的Example驱动源码,这些代码往往是经过验证的,可以事半工倍,即使有小的Bug,其官网或者网络上也基本都有其对应的解决方法。

版权声明:本文为博主原创文章,遵循 CC 4.0 BY-SA 版权协议,转载请附上原文出处链接和本声明。

本文链接: https://blog.csdn.net/wrong_jian/article/details/103878236