本文转载自: 无界逻辑(微信号:wujieluoji)微信公众号

异步FIFO通常用于跨时钟域处理,是逻辑设计常用基础模块。

一,异步FIFO结构及特点

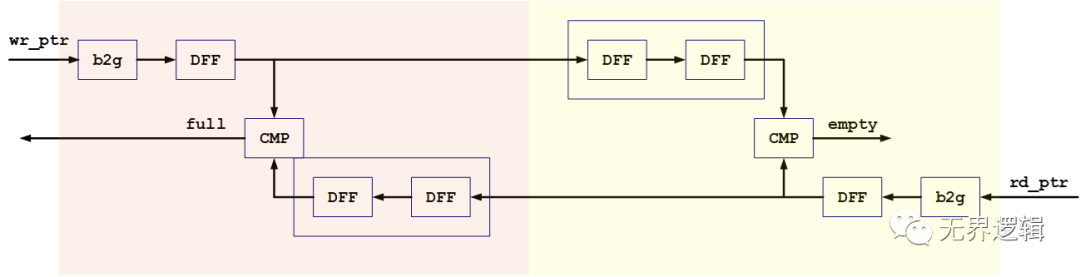

异步FIFO也分为三个部分:FIFO写控制逻辑,FIFO读控制逻辑以及FIFO存储实体。这里作者习惯使用push(等同写)pop(等同读)来表述FIFO的概念。

需要特别注意异步FIFO的特点

二,空满产生方案(二进制对比)

FIFO空满状态产生判断只能使用方法二。

1.wr_ptr跨时钟域到wr_ptr_pop的处理过程为:

2.rd_ptr跨时钟域到rd_ptr_pop的处理过程为:

三,优化方案:格雷码对比,产生空满

电路优化:我们可以使用格雷码进行对比,产生空满信号,时序和时延都会得到改善。

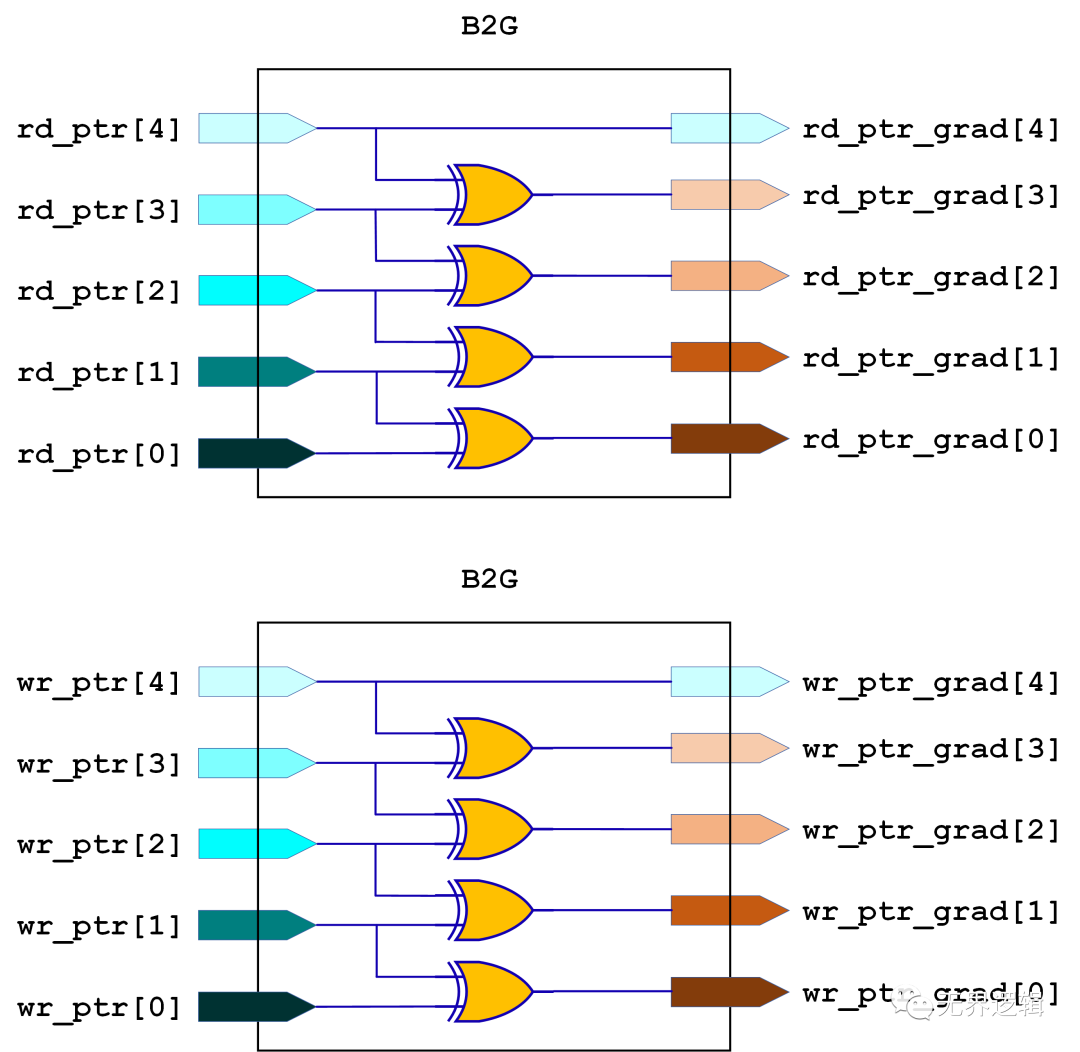

1.空状态判断

二进制数值判断条件:rd_ptr == wr_ptr_pop

等价于<=>

格雷码数值判断条件:rd_ptr_grad == wr_ptr_pop_grad

可参考下图的格雷码变换

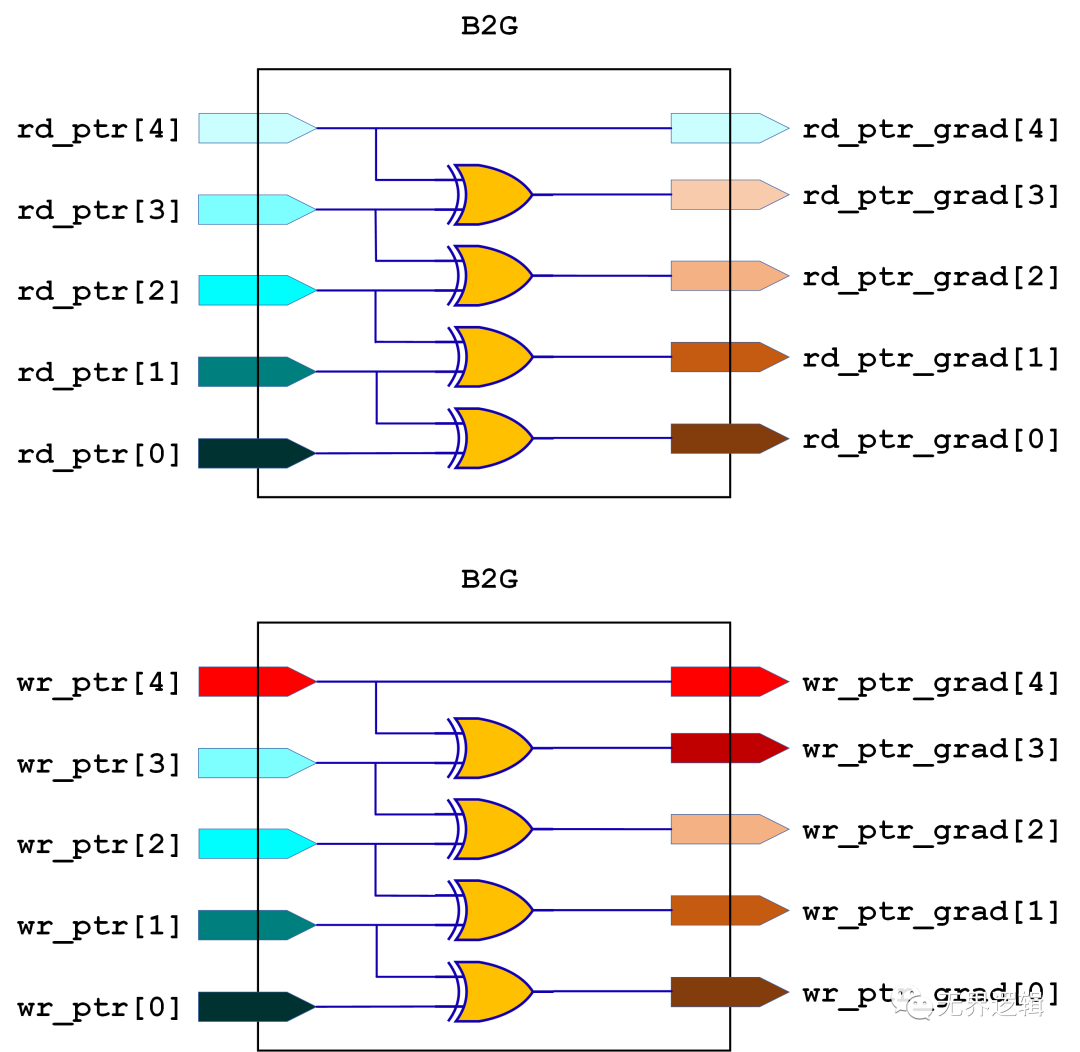

2.满状态判断

二进制数值判断条件:wr_ptr[4] == !rd_ptr_push[4] &&

wr_ptr[3:0] == rd_ptr_push[3:0]

等价于格雷码数值判断:

wr_ptr_grad[4] == !rd_ptr_push_grad[4] &&

wr_ptr_grad[3] == !rd_ptr_push_grad[3] &&

wr_ptr_grad[2:0] == rd_ptr_push_grad[2:0]

如二进制最高bit不同,会使转换后的格雷码最高和次高bit值不同。 即:高两位相反,低位相同;

可参考下图的格雷码变换:

四,总结