文章来源:FpgaHome

在使用Xilinx FPGA PCIe IP核搭工程前,我们将详细介绍该IP核的使用方法。本文档主要来源于Xilinx的IP官方使用手册,主要摘录了作者认为其中比较重要以及常用的部分。大家可以把这篇文章收藏到微信中,当需要分析定位一些问题而手边又无法立马找到官方手册情形下,这篇文档可能可以应急。

很多初学者刚开始看到PCIe IP文档时,不太懂Xilinx PCIe IP核主要的数据接口:CC、CQ、RQ、RC。本文主要就是对这些接口做详细的介绍,希望能答疑解惑。

1. IP接口

Xilinx UltraScale+器件的PCIe IP核接口如下图所示:

其中黄色线框出的接口为我们要重点介绍的用户侧数据接口。

在PCIe系统中,完成器接口(Completer Interface)和请求器接口(Requester Interface)是两种主要的接口类型,各自具有不同的功能和用途。

PCIe 完成器接口 (Completer Interface)

常见用途:主要用于实现存储器映射I/O(MMIO)和配置空间访问。

PCIe 请求器接口 (Requester Interface)

通俗来讲,两个接口的主要区别是:

FPGA通过完成器接口接收CPU或PC机发来的读写请求,然后再通过完成器接口把要读写的数据回馈给PC;(FPGA处于事务被动测)

FPGA通过请求器接口向PC机主动发起读写请求,再通过请求器接口发送和接收PC机回馈的数据。(FPGA处于事务主动测)

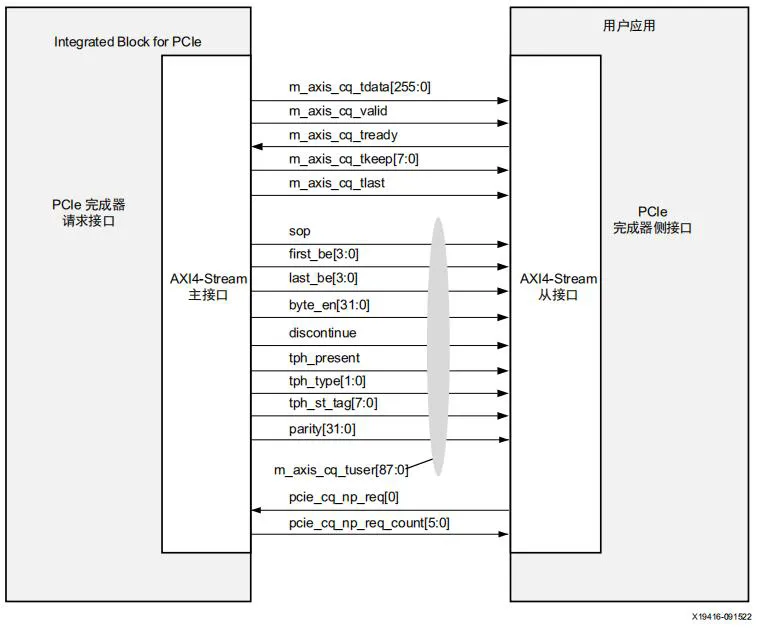

下图展示了与核的完成器请求接口相关的信号。每个通过此接口的TLP都会作为一个AXI4-Stream数据包传递。对于包含有效载荷的TLP,该数据包以128位描述符开头,后面跟随数据部分。

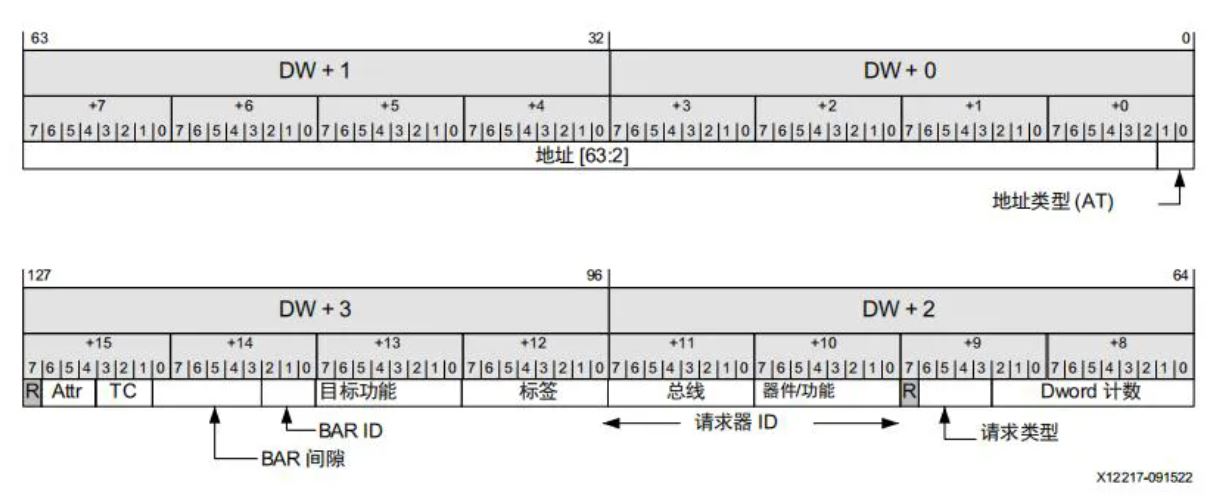

描述符的格式如下,CQ接口将从链路接收到的每个请求TLP作为独立AXI4-Stream数据包通过CQ接口进行传输。每个数据包均以1个描述符开头,在描述符后可包含有效载荷数据。描述符长度始终为16字节,并在请求包的前16字节内发送。

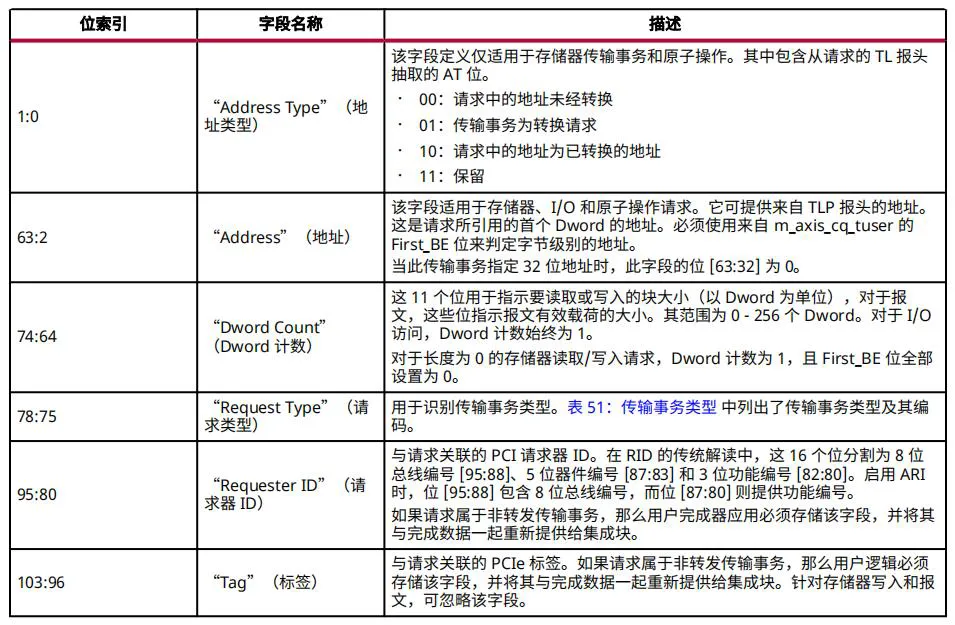

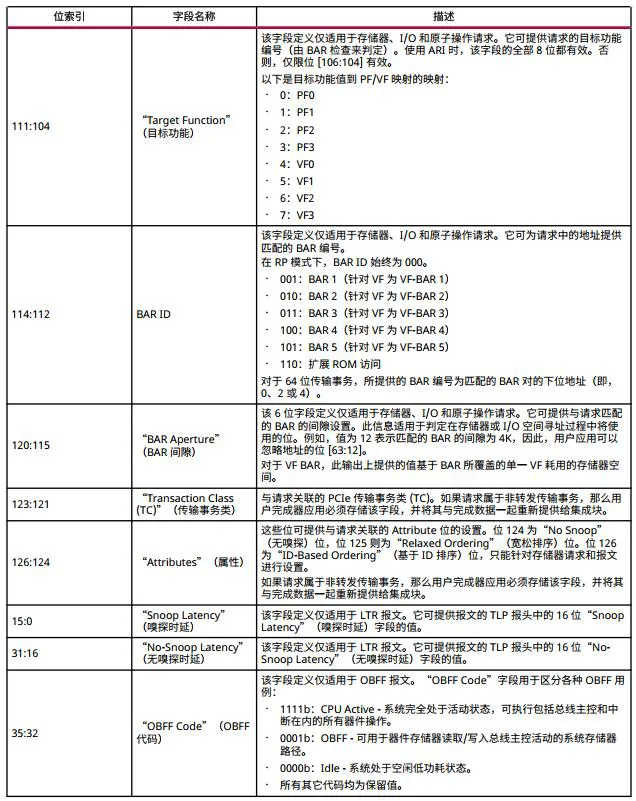

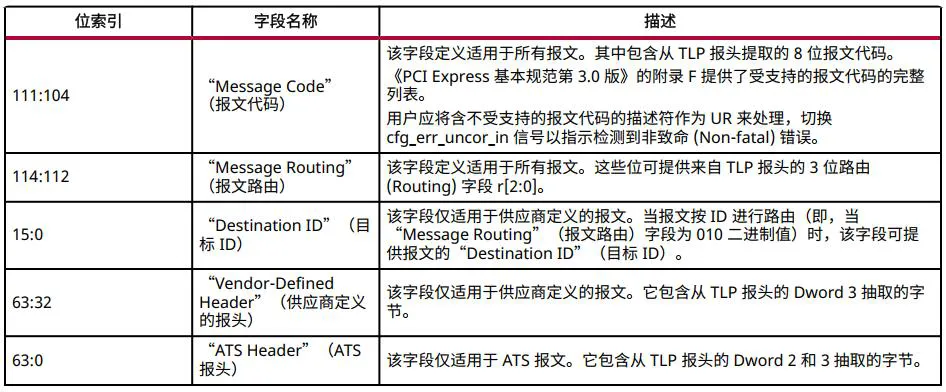

完成器请求(CQ)描述符字段表:

传输事务类型:

CQ接口的写入操作

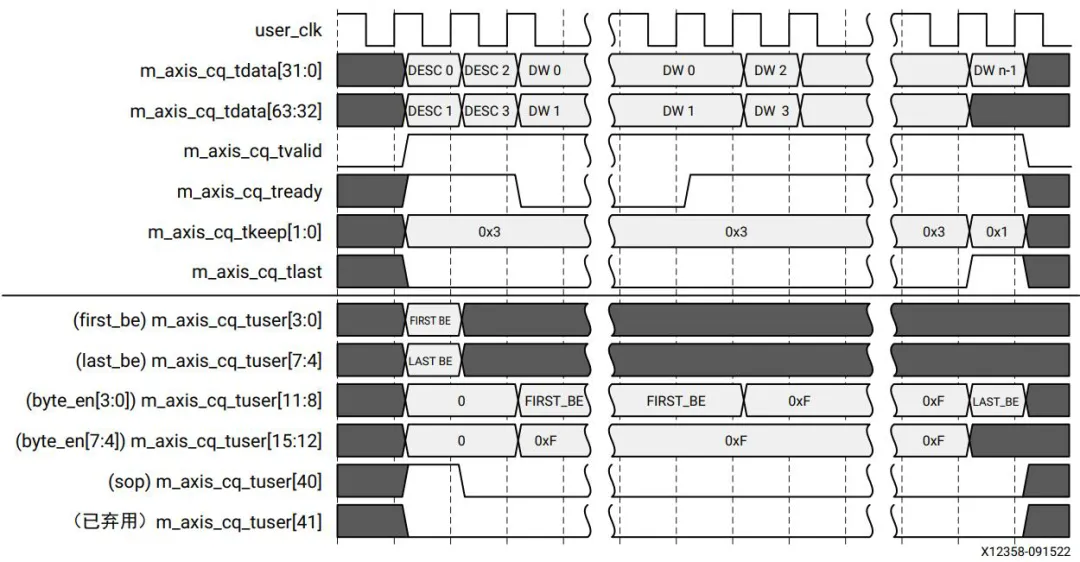

以下时序图显示了当接口宽度分别配置为 64 位时,从链路接收到存储器写入TLP(采用 Dword对齐模式)后,通过完成器请求(CQ)接口来进行传输的过程。

在Dword对齐模式和地址对齐模式下,传输均从16个描述符字节开始,紧随其后即为有效载荷字节。在数据包持续时间段内,m_axis_cq_tvalid信号保持处于断言有效状态。您可随时通过使用deasserting m_axis_cq_tready断言此信号无效来延长任一节拍。

CQ 接口在m_axis_cq_tuser总线中还包含“First Byte Enable” (首字节使能) 位和“Last Byte Enable”(末字节使能)位。这些位在数据包的第一拍内有效,并用于指定有效载荷的第一个和最后一个Dword的有效字节。

CQ接口的读取操作

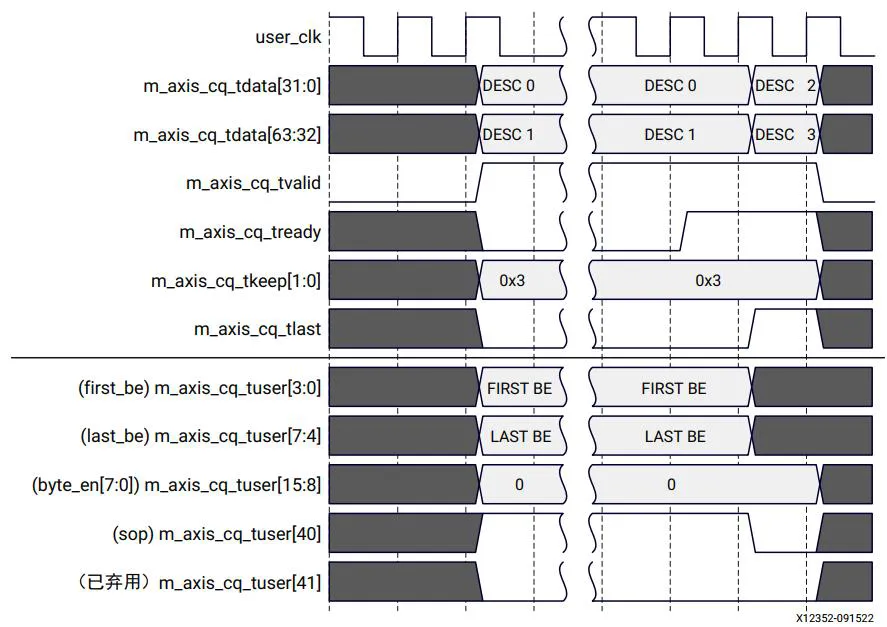

存储器读取请求跨完成器请求接口进行传输的顺序与存储器写入请求相同,除非AXI4-Stream 数据包仅包含16字节描述符。以下时序图显示了当接口宽度分别配置为64位时,从链路接收到存储器读取TLP后,通过完成器请求接口来进行传输的过程。

2.2完成器完成接口 (CC Interface)

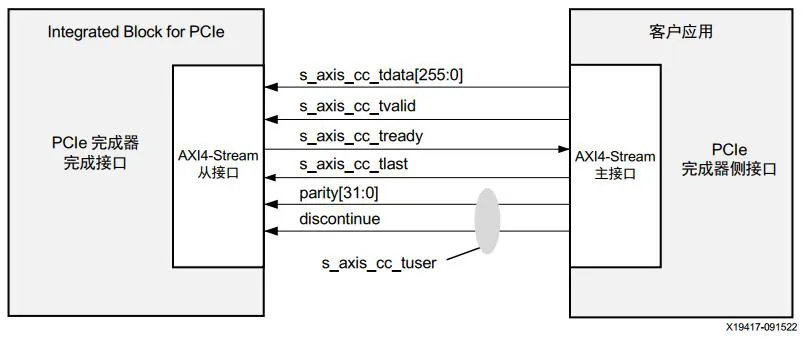

下图显示了与核的完成器完成接口关联的信号。核将此接口上的每个TLP均作为1个 AXI4-Stream数据包来交付。

每个数据包均以1个描述符开头, 在描述符后可包含有效载荷数据。描述符长度始终为12字节,并在完成包的前12字节内发送。描述符的格式如下:

完成器完成接口(CC)描述符字段表:

每次从完成器请求(CQ)接口接收到1个非转发请求时,用户应用都必须向核的CC接口返回1个完成(Completion)包。当请求完成且不含任何错误时,用户应用必须返回含成功完成(SC) 状态的完成包。

根据请求类型,此完成包可能包含有效载荷,也可能不含有效载荷。此外,当数据块大小超出配置的有效载荷最大大小时,与请求关联的数据可拆分为多个拆分完成(Split Completion)包。用户逻辑负责根据需要将数据块拆分为多个拆分完成包。用户应用必须将每个拆分完成包作为独立 AXI4-Stream数据包(包含其自己的 12 字节描述符)通过完成器完成接口进行传输。

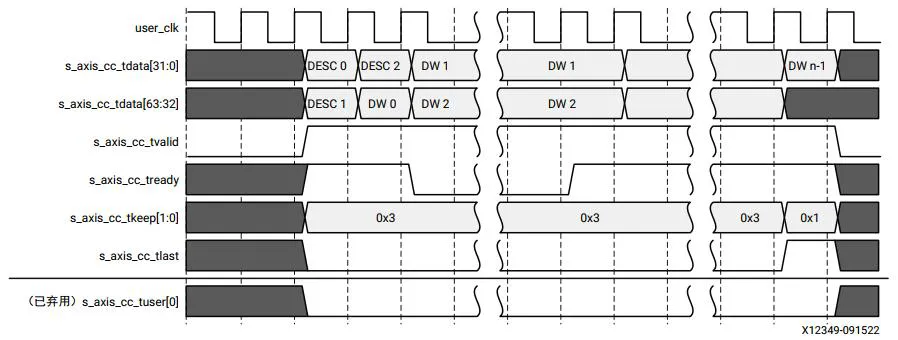

以下时序图显示了当接口宽度分别配置为64位时,Dword对齐模式下,CC接口的时序图。

2.3请求器请求接口 (RQ Interface)

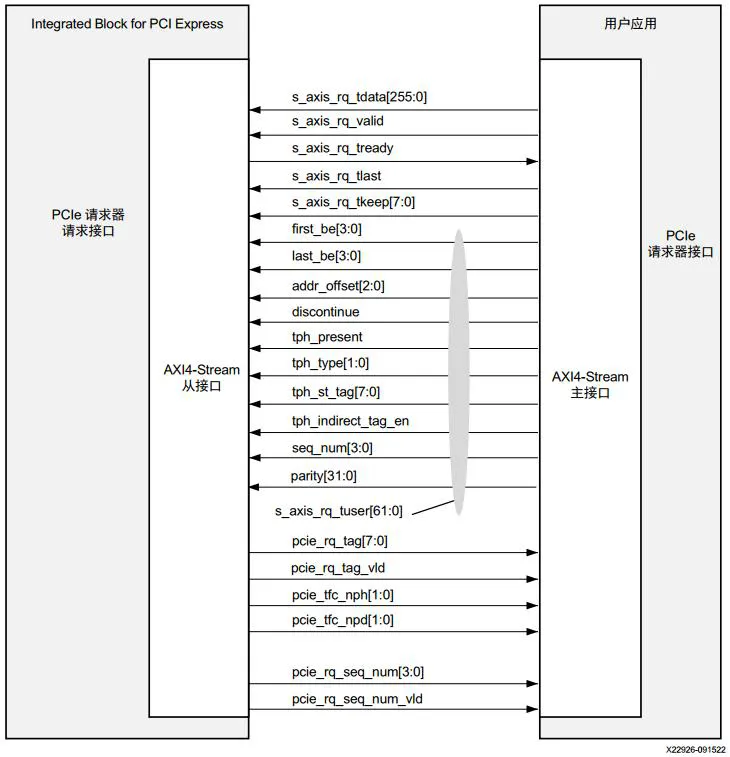

在RQ接口上,用户应用将每个TLP都作为1个AXI4-Stream数据包来进行交付。对于含有效载荷的TLP,此数据包以128位描述符开头并后接数据。下图显示了与请求器请求接口关联的信号。

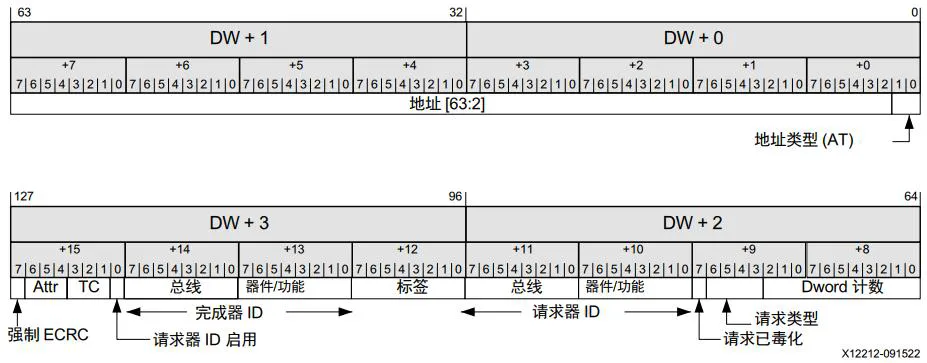

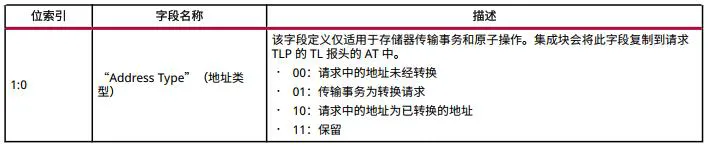

描述符的格式如下:

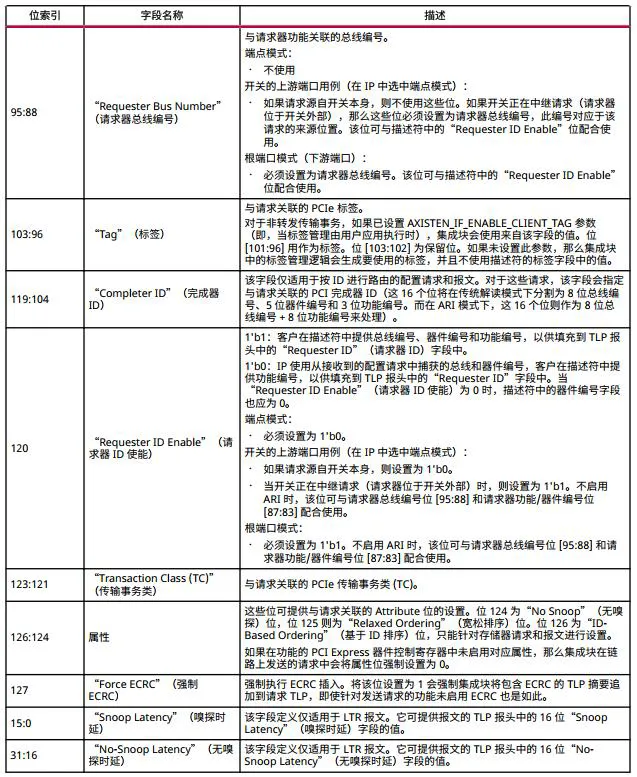

请求器请求接口(RQ)描述符字段表:

RQ接口的写入操作

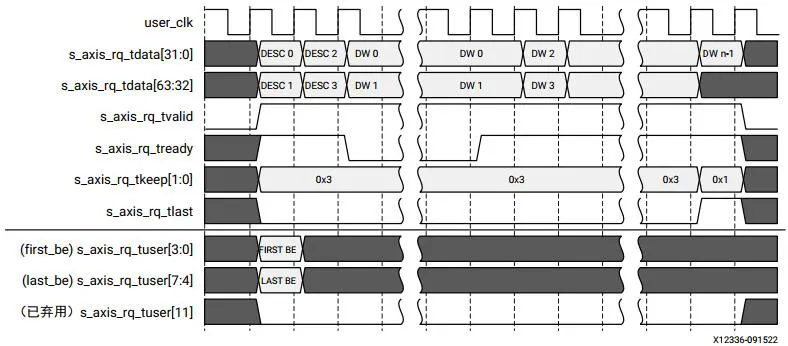

在Dword对齐模式下,传输从16个描述符字节开始,紧随其后即为有效载荷字节。用户应用必须在数据包的整个持续时间段保持s_axis_rq_tvalid信号处于断言有效状态。集成块会将数据包传输期间断言无效的s_axis_rq_tvalid 作为错误来处理,并将链路上发射的对应请求TLP置空,以避免数据损坏。

RQ接口的存储器读取请求操作

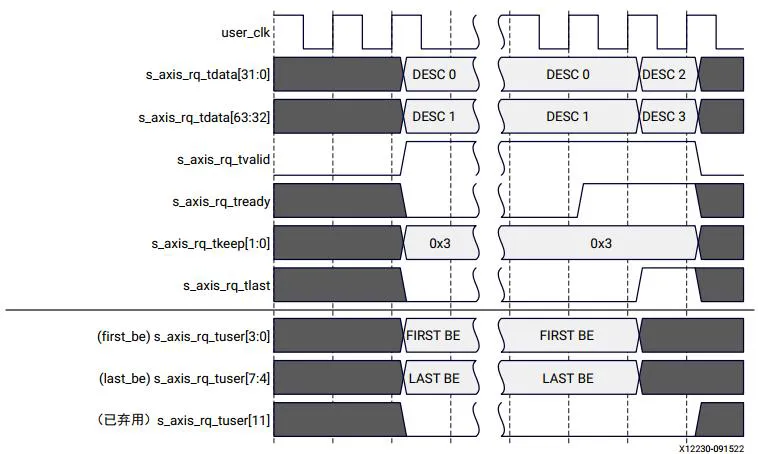

不含有效载荷(存储器读取请求、 I/O 读取请求、配置读取请求)的非转发传输事务将按存储器写入请求相同的方式跨RQ接口进行传输,但区别在于AXI4-Stream数据包仅包含16字节描述符。以下时序图显示了当接口宽度分别配置为64位时,通过RQ接口来传输存储器读取请求的过程。

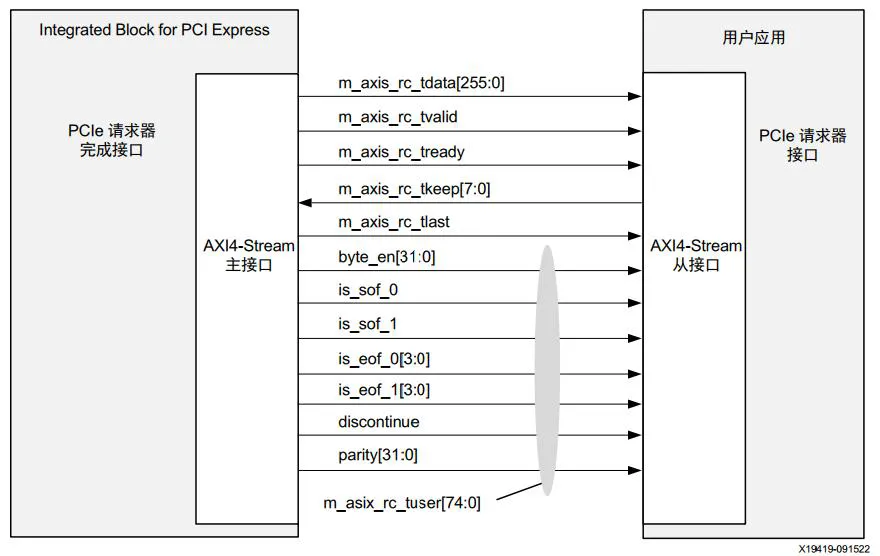

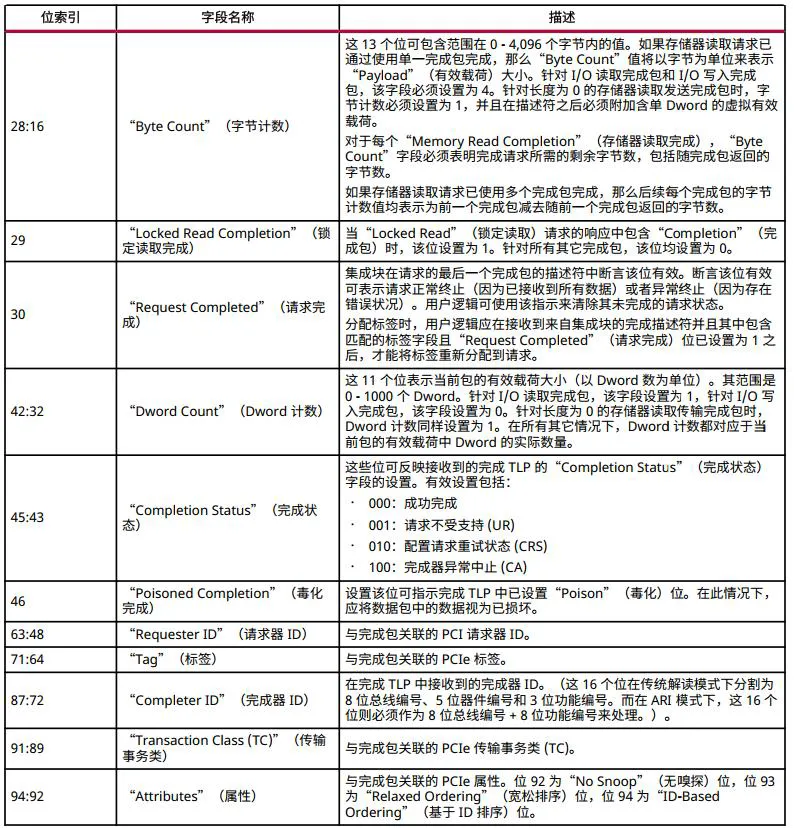

2.4请求器完成接口 (RC Interface)

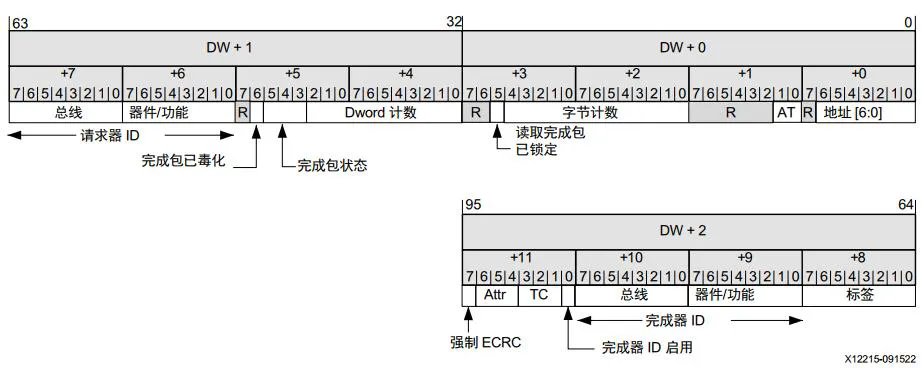

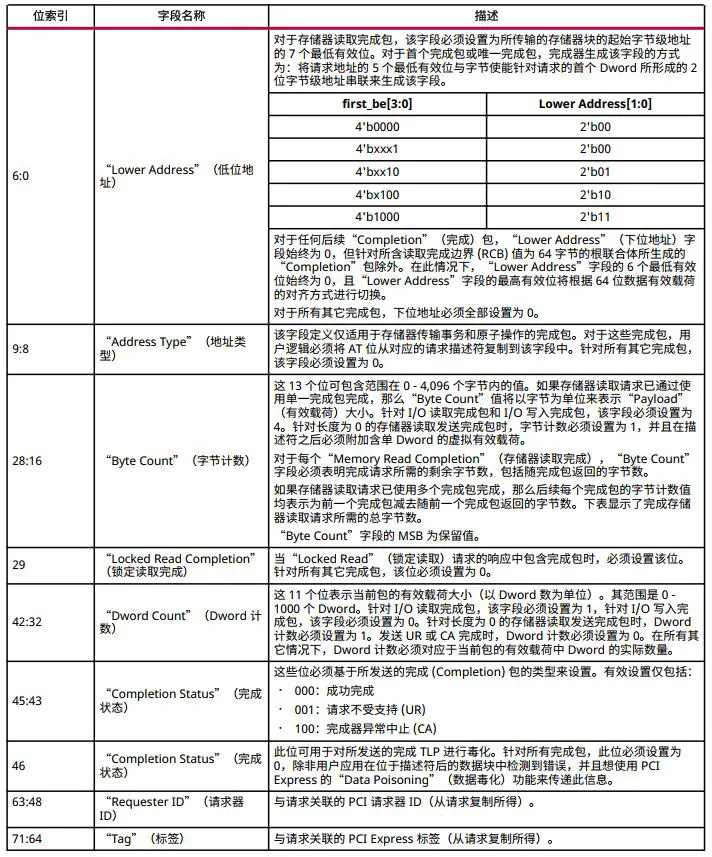

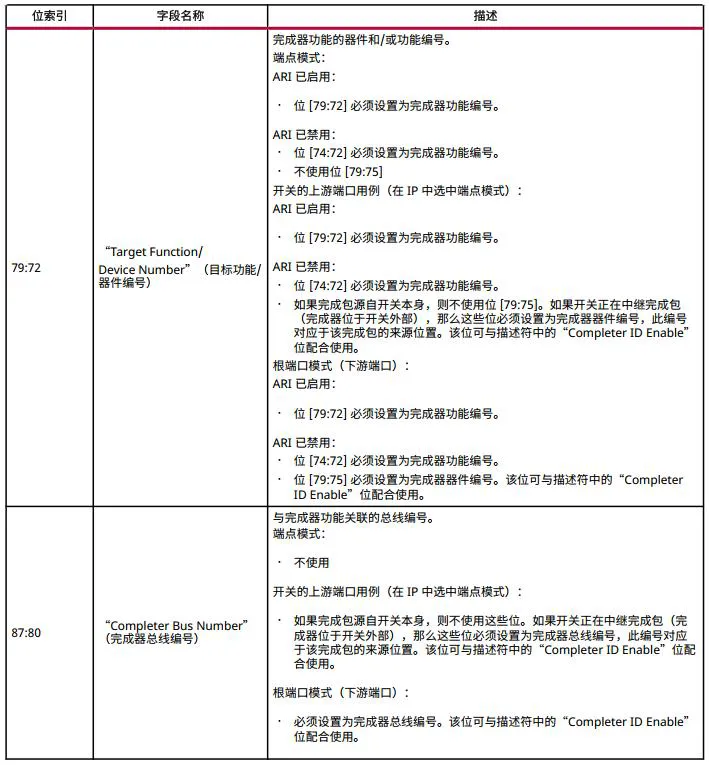

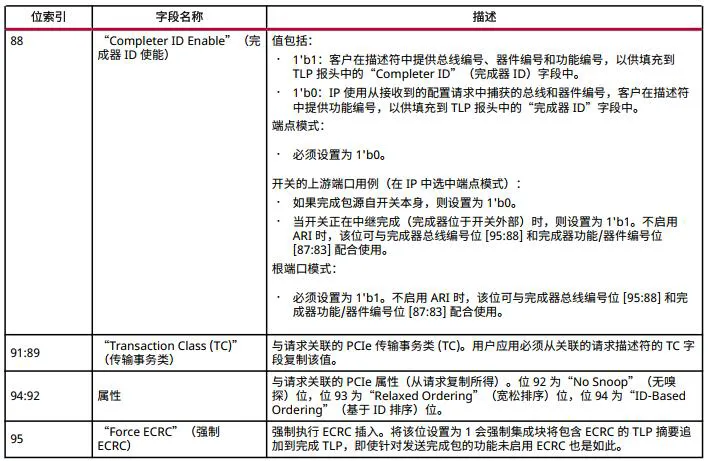

当用户逻辑生成的请求完成时,结果会显示在IP的请求完成 (RC) 接口上。请看下图,图中展示了与请求完成接口相关的信号。IP会将接口上的每个传输层数据包 (TLP) 作为一个 AXI4-Stream 数据包传输。对于含有有效载荷的数据包,这个数据包以96位描述符开头,然后紧接着是数据。

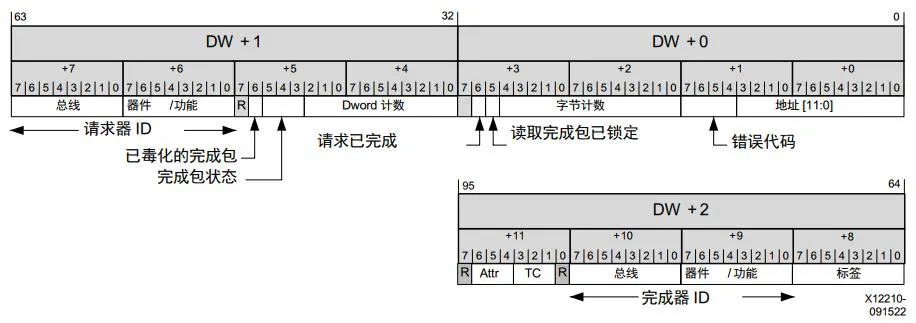

描述符的格式如下:

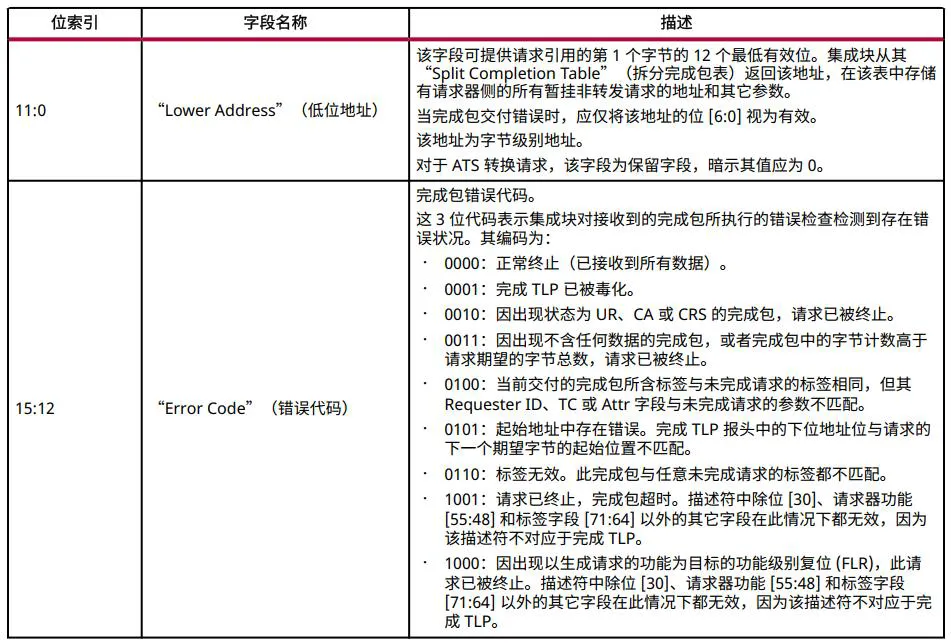

描述符各个字段的含义如下:

RC接口工作在Dwords对齐模式下,时序如下图所示:

3.总结

本文向大家初步介绍了下Xilinx PCIe IP核的主要接口细节。更详细的IP使用说明还需参考官方文档。下次更新我们将讲述如何使用该IP搭一个FPGA PCIe工程。如果觉得我们的文章写的还不错,帮忙点赞和推荐吧,谢谢您的关注。

[1] Ultrascale+ integrated block for pci express v1.3, Xilinx, PG213