本文转载自:FPGA入门到精通

今天介绍一下非常好用的 Vivado DDS IP 核。

一、什么是 DDS IP 核

DDS 即直接数字频率合成(Direct Digital Frequency Synthesizer),它是一种基于全数字技术,从相位概念出发直接合成所需波形的频率合成技术。

简单来说,DDS 可以根据我们设定的参数,快速、准确地生成各种频率的正弦波、余弦波等波形信号。

而 Vivado DDS IP 核则是 AMD(Xilinx) 公司在 Vivado 开发环境中提供的一个功能强大的 IP 核,用于实现 DDS 功能。

二、Vivado DDS IP 核的基本架构

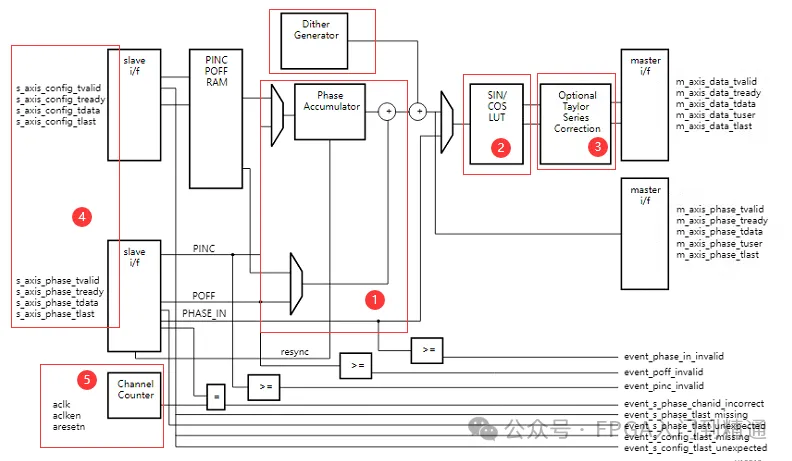

从上图中可以看出,Vivado DDS IP 核主要由以下几个部分组成:

1、相位累加器

这是 DDS IP 核的核心部件之一,它按照系统时钟的频率不断累加相位。

就像一个不断前进的时钟,每走一步就代表相位增加了一定的值。

相位累加器输出的结果作为查找表的地址。

2、查找表(LUT)

查找表中存储了预先计算好的正弦波或余弦波的数值。

当相位累加器输出地址后,查找表根据该地址输出对应的正弦波或余弦波的数值,从而实现波形的生成。

3、抖动产生器和泰勒级数矫正产生模块

主要用于改善无杂散动态范围(SFDR)。

抖动产生器通过产生随机的噪声来使得量化误差随机化,从而提高 SFDR;

泰勒级数矫正则是利用泰勒级数展开的方法对相位误差进行矫正,提高信号的质量。

不过,两者改善的效果和使用的逻辑资源存在差异。

4. AXI4 接口

用于实现相位累加字配置、多通道配置、相位累加器输出和波形数据输出等功能,方便与其他 IP 核或模块进行通信。

5. 多通道输出模块(可选)

在需要同时生成多个不同频率的波形信号时,可以使用多通道输出模块。

每个通道都可以独立地配置输出频率、相位等参数。

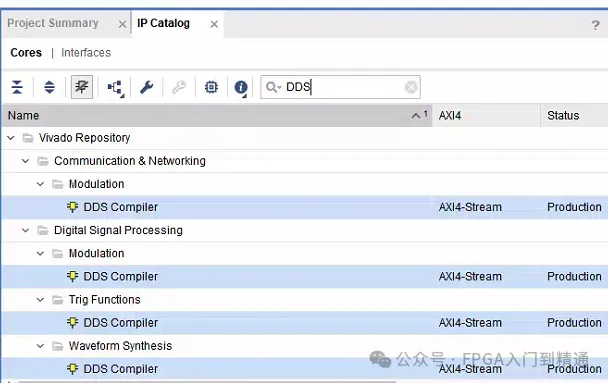

三、Vivado DDS IP 核的参数配置

在vivado中,打开ip catalog,找到DDS ip 核,鼠标双击进入配置页面,如下图。

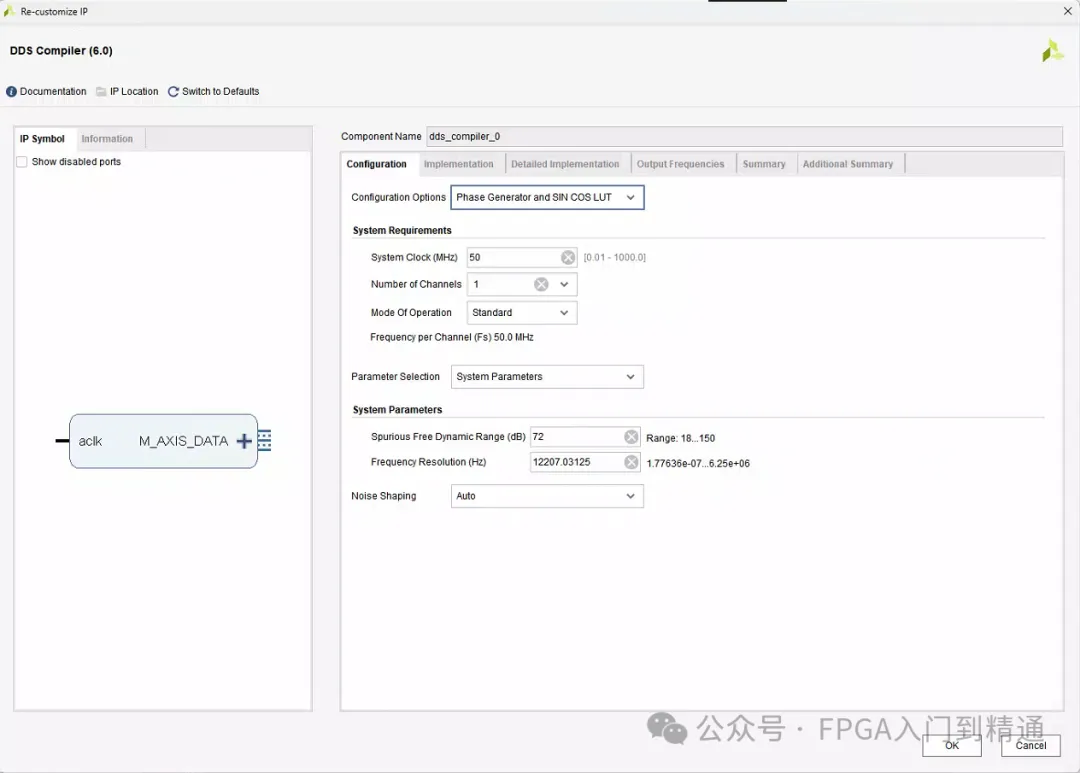

1、configuration页面

(1)Configuration Options

Phase Generator and SIN/COS LUT (DDS):相位和sin和cos的数据都是IP核自己产生

Phase Generator only:只要相位输出

SIN/COS LUT only模式:只需要sin/cos模块输出,但此模式需要外部不断的输入累加的相位

(2)System Requirements

System clock 系统时钟频率,同样也是采样率

Number of channels 通道数

Mode of operation 操作模式,一般选择standard。

(3)parameter Selection

可选System Parameters 或Hardware Parameter,一般使用System Parameters。

选择System Parameters时,可以直接设置无杂散动态范围、频率分辨率、输出频率等系统级的参数。

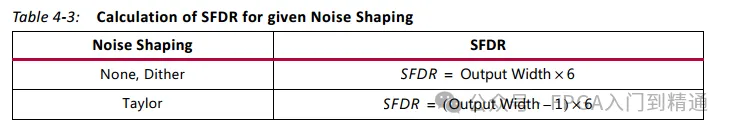

SFDR:

无杂散动态范围,参考PG141, SFDR 设置信息为:

例如输出位宽为14,Noise Shaping选择为 Taylor Series Corrected时,SFDR = 6*14-1 = 83。

Frequency Resolution:

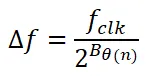

Standard Mode of Operation标准操作模式

说明:fclk是系统时钟频率,Bθ是相位宽度,Δf 是频率分辨率。

单通道输出,则单个通道驱动时钟64MHz(若输出N个通道,则计算时每个通道驱动的时钟为Fclk /N。)

Fr = 64_000_000/2^14 = 3906.25(小数点后面数字必须全部保留)

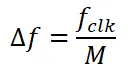

Rasterized Mode of Operation栅格化操作模式

说明:fclk是系统时钟频率,M是模数,Δf 是频率分辨率。

选择Hardware Parameter时,需要设定输出数据和相移的位宽,输出频率、相位偏移等值需要自己计算对应的二进制数值。

相位宽度(Phase Width):相位宽度决定了相位累加器的位宽,也就是相位的精度。相位宽度越大,相位的精度就越高,能够生成的波形就越细腻,但同时也会消耗更多的逻辑资源。

输出宽度(Output Width):输出宽度决定了查找表输出的正弦波或余弦波数据的位宽,也就是波形的幅度精度。输出宽度越大,波形的幅度精度就越高,但同样会消耗更多的逻辑资源。

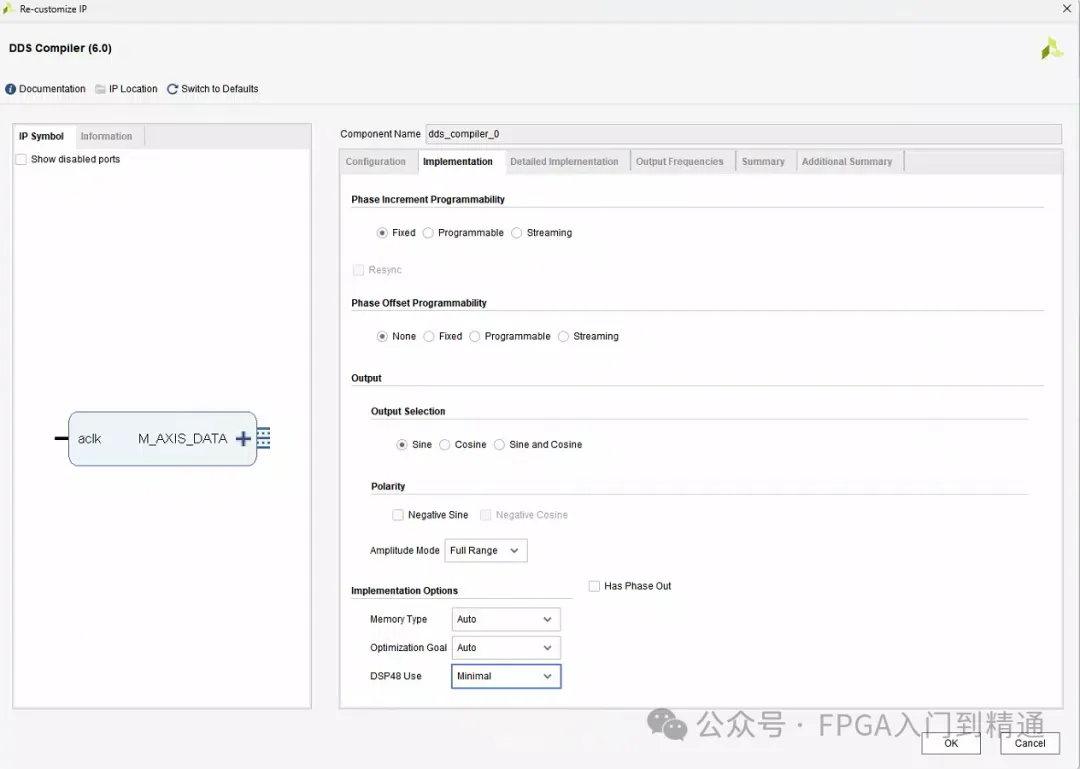

2、Implementation页面

(1)Phase Increment Programmability

相位增量(即频率控制字)控制模式选择,可选固定(Fixed)、可编程模式(Programable)、流式(Streaming)。

如果选择固定模式,在Output Frequencies页面可配置输出的频率。

如果选择可编程模式,模块会新增一个配置参数接口,可通过程序配置。

(2)Phase Offset Programmability

相位偏移量(即相位控制字)控制模式选择,可选无(NONE)、固定(Fixed)、可编程模式(Programable)、流式(Streaming)。

(3)Output

输出选择设置,可选sin、cos、sin&cos。

polarity极性设置,可选Negative sine、Negative cosin。

Has Phase Out,选择是否输出相位。

(4)Implementation Options

Memory Type:存储使用资源选择,auto表示自动选择,Distributed Rom、Block Rom。

Optimization Goal:布线优化目标选择,auto表示自动选择,area表示面积优先,speed表示速度优先

DSP48 Use:使用DSP资源的策略。

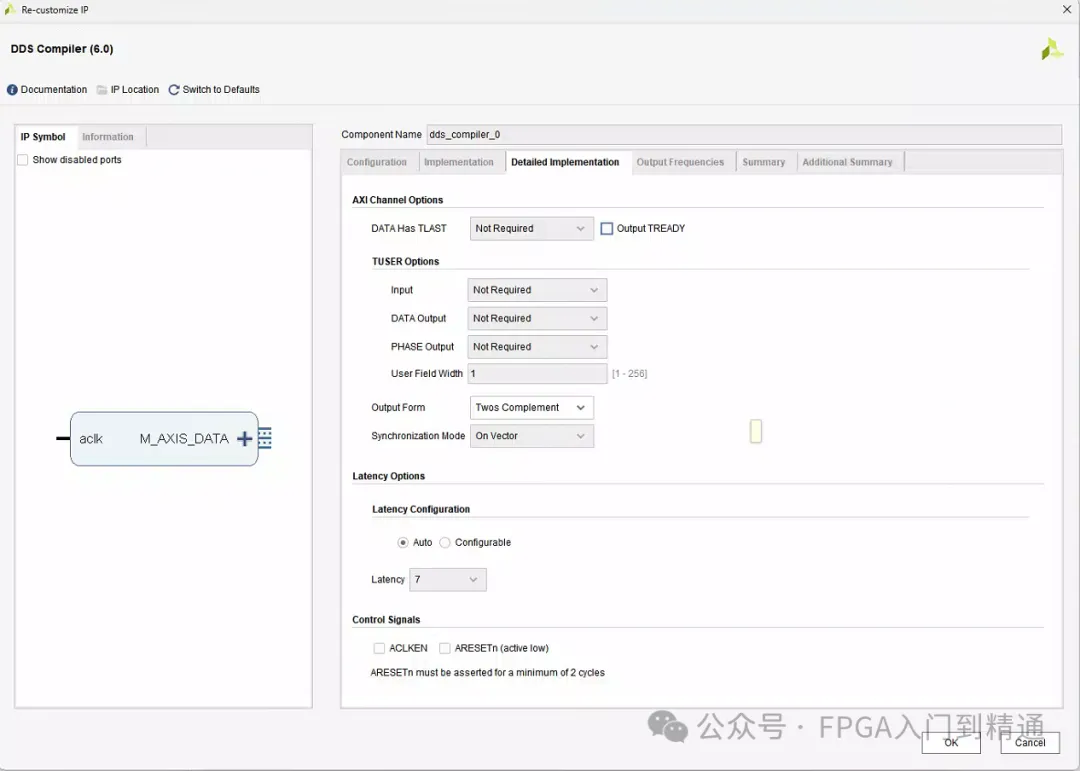

3、Detailed Implementation页面

设置输入输出的相关信号,包括tlast、tuser等等。

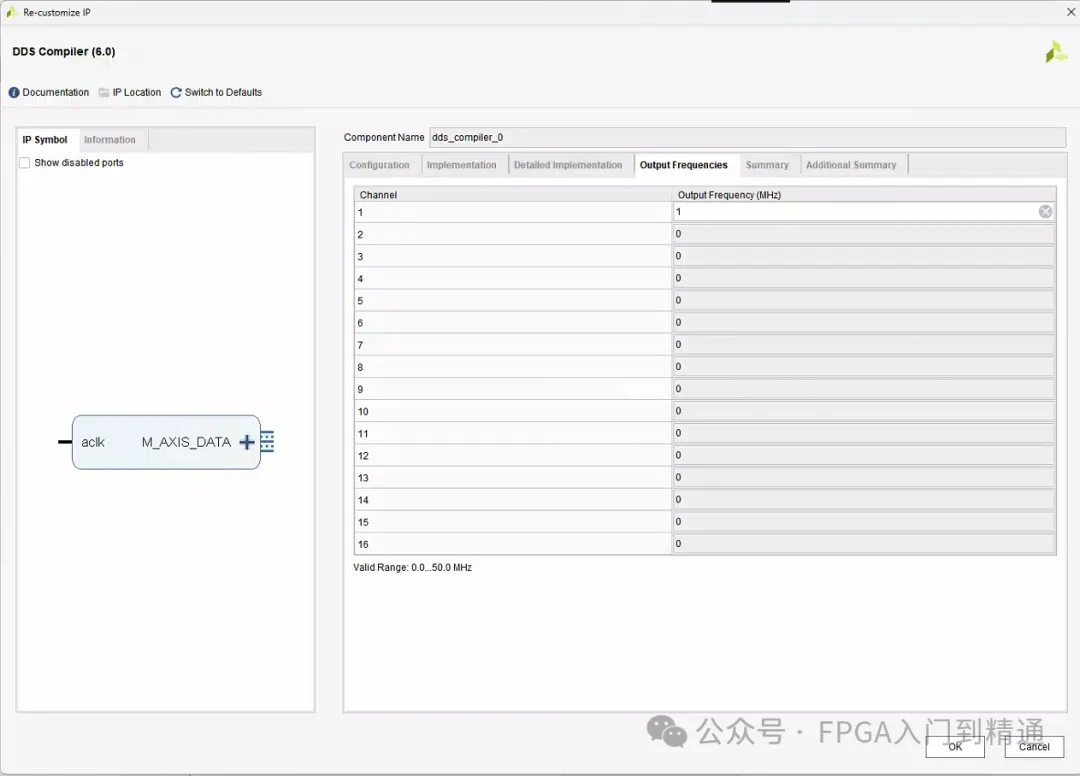

4、Output Frequencies 页面

输出频率设置,选择System Parameters时,需要设置。

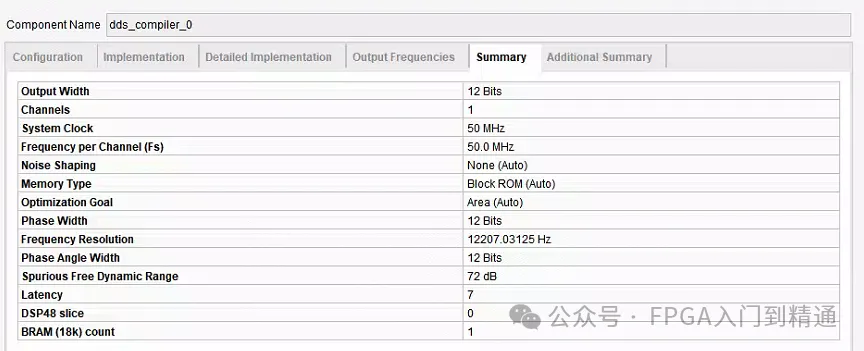

5、Summary

信息汇总,可检查配置的参数是符合要求。

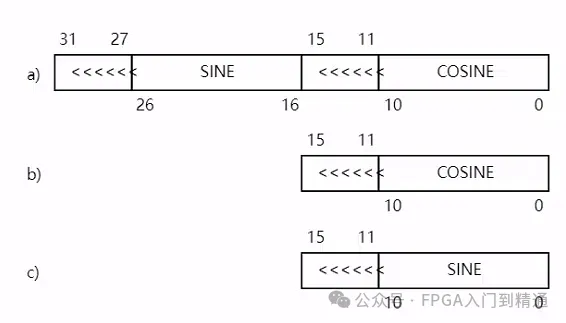

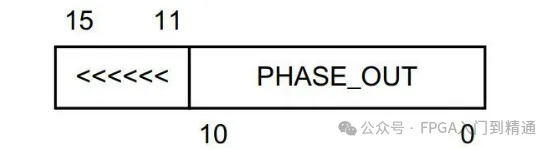

四、注意输出数据位宽问题

IP核的位宽只会是8的倍数,多余的位数会移符号为填充。

设置为“Sine and Cosine”输出时,sin和cos信号共用数据总线,sin使用高字节,cos使用低字节,格式如下: