7.2.2 细频率校正

经过粗频率校正(CFC)后,仍存在基于所配置分辨率fr的频率偏移。细频率校正(FFC),又称载波相位校正,应当产生稳定星座,以供最终解调使用。

本质上,该校正将使接收信号的剩余频率偏移趋近于零。我们可以将此校正描述为产生稳定星座,因为频率偏移的细微影响通常通过星座图进行分析。如果一个

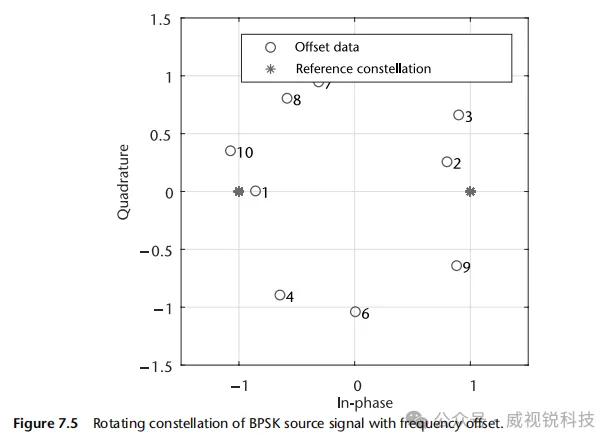

离散数字调制信号存在频率偏移时,会导致信号随时间产生旋转,如星座图中所示。在图 7.5 中,我们演示了该效应,图中每个数字对应样本在时间上的相对出现顺序,揭示了旋转的动态过程。信号本身为二进制相移键控(BPSK),导致其在不同源符号下穿越星座图原点跳变。当施加正频率偏移时,旋转为逆时针方向;而施加负频率偏移时,旋转为顺时针方向。

旋转速率即为频率偏移,这正是我们在(7.3节)中定义的ω(角频率)的来源。

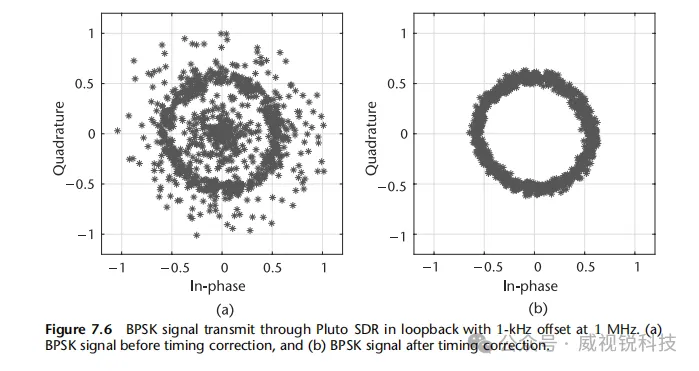

该频率偏移也可通过Pluto软件定义无线电以类似方式观测。图7.6中,我们发射了一路BPSK信号回环,发射和接收本振集合之间存在1千赫兹的差异。在图7.6(b)中见到了与图7.5中类似的旋转现象。为了正确显示该效应,需进行时序校正,该方法借鉴自第6章节。未进行时序校正时,如图7.6(a)所示,星座图上的信号难以解读。此处因先进行了时序校正,然后才进行频率校正,因此使用了6.4.1节详述的Gardner技术。与CFC不同,

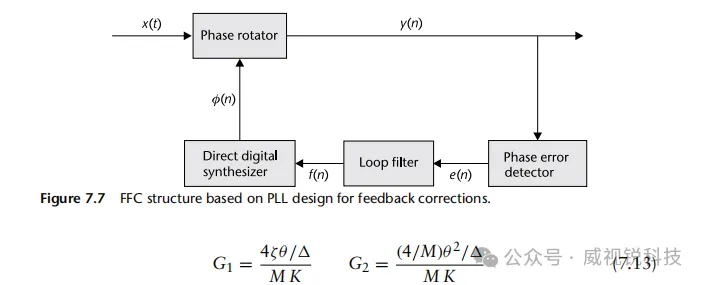

本方法采用前馈技术,对于FFC,我们将基于第4章节锁相环理论,采用反馈或闭环方法。该算法结构如图6.11所示,并与我们原始图6.11中的框架相对应。

该全数字锁相环算法首先在相位误差检测器(PED)中测量接收样本的相位偏移,称为误差信号e(n)。 相位误差检测器的设计基于目标接收星座/符号的结构。接下来,环路滤波器有助于控制整个锁相环(PLL)的动态特性。该环路滤波器可以决定工作频率(有时称为捕获范围)、锁定时间和PLL的响应速度,并平滑误差信号。最后,数字直接合成器(DDS)则继承自采用压控振荡器(VCO)的模拟PLL设计。DDS负责生成输入信号的校正信号,该信号将反馈至系统。对于FFC设计,该锁相环最终应输出偏移量为零的期望信号。

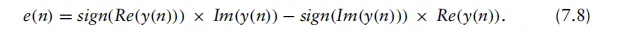

从脉冲误差检测(PED)模块开始,其目标仅是测量输入复数数据相对于期望参考星座的相位或径向偏移。通过参考以及推广e(n),我们实际上指的是与星座基点之间的距离。对于QAM、PSK和PAM调制,这些基点将始终是实轴和虚轴。然而,针对FSK或其他调制方案,您可能需要扩展此视角。该观点的核心在于消除某一特定维度的缩放因素,而改为考察特定基底中能量或振幅的比值。为更好地理解此概念,我们考虑QPSK,其具有以下脉冲误差检测(PED)方程:

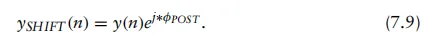

在(7.8)中,e(n) 本质上衡量了y(n)的实部与虚部的差异,仅当Re(y(n))=Im(y(n))时才为零。您会注意到,这将使输出星座仅限定于特定方向,而非特定范数值。然而,若y(n)需不同方向,则可在经同步器之后,通过与所需φPOST相位移的简单相乘来实现,表达为

请注意, ySHIFT (n)不应输入至脉冲误差检测(PED)模块。

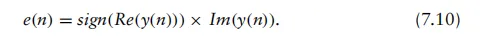

其他调制方案中,PED误差估计将依据期望的信号排列而变化。例如,二进制相移键控(BPSK)或脉幅调制(PAM)具有以下误差估计:

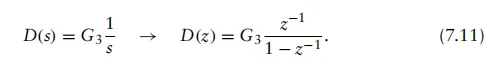

该PED误差函数的目标依旧是仅为y(n)的方向提供误差信号。对于(7.10), e(n)仅当y(n)为纯实数时才为零。(7.8)和(7.10)背后的推理十分直接。另一方面,所有PLL设计中最具挑战性的部分是环路滤波器,但它对系统自适应提供了最大的控制。这里我们再次采用第6.3.1节中详细介绍的PI滤波器作为环路滤波器。这一FFC同步器的最后部分是DDS,它仅为一个积分器。由于环路滤波器产生的控制信号与输入信号的频率等效,因此必须改为提取该信号的相位。此处积分器所用的传递函数为

请注意,我们在离散域中增加了一个单样本的额外延迟,因为我们正在产生一个校正信号G3=−1。该积分器同样可以通过双二阶滤波器实现。

在图7.7所示的锁相环配置中,系统应产生输出y(n),该输出具有极小的相位和频率偏移。沿图7.7中的环路再次运行时,脉冲误差检测器首先产生一个误差,该误差等于观察到的校正符号1symbol y(n)所对应的相位偏移,随后环路滤波器将该误差与之前所有误差加权关联。最后,数字直接合成器将加权的误差/控制信号 f(n)转换为相位φ(n),用以校正下一输入样本 x(n+1)。 在存在频率偏移的情况下,φ会持续变化,因为它是一个相位值,而非频率值。然而,如果输入信号过于动态或滤波器的增益值设置不当,锁相环将无法跟上 x变化的相位(频率)。

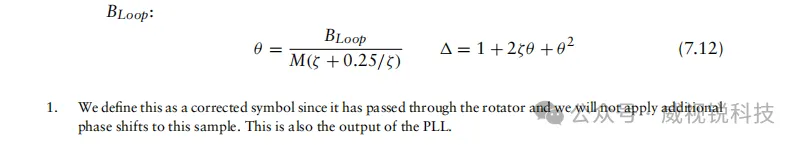

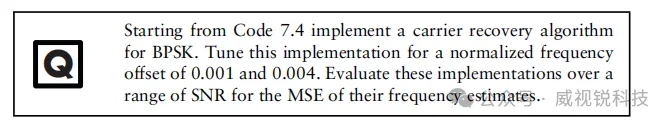

环路滤波器的增益值(G1,G2)计算可利用以下基于首选阻尼因子ζ和环路带宽的方程。

其中,M为每符号样本数,K为探测器增益。对于QPSK和矩形正交振幅调制,K=2;而对于PAM和PSK,K=1。注意,B环路为归一化频率。若您有兴趣了解其推导过程,请参阅文献[6附录C]中的详细分析。关于ζ的选择,请参阅第6.3.1节,其定义与此处相同。B环路的选择应与最大估计归一化频率锁定范围f及所需锁定范围相关:

请注意,该值是基于锁相环(PLL)线性化模型的估计值。因此,模拟版本中可能存在不一致之处。然而,当配置正确时,该PLL设计在强噪声条件下仍能表现良好。与CFC校正不同,FFC通常不会具有相同的工作范围。在设计中,建议初始阻尼因子ζ=1,环路带宽BLoop=0.01。根据经验,此处使用过阻尼系统更为合适,因为它能直接扩展捕获范围。

不过这将使环路收敛时间延长。

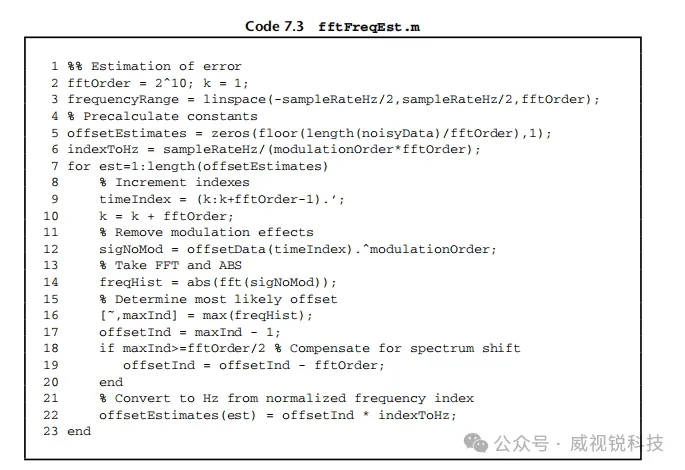

我们现已具备实现FFC同步器的所有必要组件,代码7.4中提供了完整的参考实现。然而,讨论若干设计考量仍十分必要。首先,我们已经说明FFC同步器的输出可具有特定方向的目标星座,该方向完全由脉冲误差检测(PED)决定。然而,同步器可能无法始终实现该目标星座方向,导致星座图出现轻微旋转,或位于预期位置的倍数位置。这种情况通常源于信号的载波偏移超出FFC配置可处理的范围,或最明显的是当系统配置为欠阻尼状态时。另一方面,若接收信号的信噪比较差,

每K个样本进行一次校正。理想情况下,fˆo保持不变,但若偏移接近FFT频点边界,则不太可能如此。导致信号频率相对于先前信号出现 ±fr的跳变。不幸的是,这些突变会干扰下游反馈算法,而这些算法难以应对所估计或校正信号频率或相位的突变。为解决此问题,我们采用两种主要策略。第一,可以利用滤波器对估计值进行时间平均,平滑变化过程。第二,仅在帧起始时应用此校正。因为偏移在合理长度的帧内相对稳定,单次测量即可在该时间段内保持较高准确度。该校正也被称为粗频率校正,因为其精度只能达到fr的范围,这限制了此类校正的间隔。

然而,这种基于FFT的技术的缺点是需要大量数据才能获得合理的估计。该技术在发射机采用过采样及发射滤波器时,也会产生不纯净的频率成分。但诸如Luise[5]等其他技术是为突发式应用设计的,相比上述FFT方法所需的数据量更少。

遗憾的是,Luise方法是有偏估计,而FFT方法则是无偏估计。

文章来源:威视锐科技