MIPI CSI-2 Receiver Subsystem应用总结

judy 在 周三, 04/27/2022 - 10:02 提交

在进行MIPI摄像头开发时,经常用到Xilinx的MIPI CSI-2 Receiver Subsystem IP,下面对该IP使用方法进行简单介绍。

在进行MIPI摄像头开发时,经常用到Xilinx的MIPI CSI-2 Receiver Subsystem IP,下面对该IP使用方法进行简单介绍。

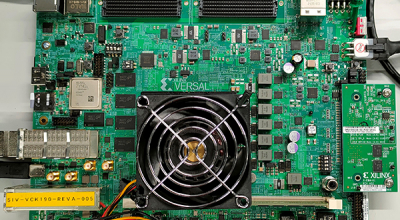

本章旨在演示如何基于 Versal™ 来构建同时使用 SmartLynq+ 模块和高速调试端口 (HSDP) 的系统。

report_clock_interaction矩形框内的不同颜色表征了不同时钟域之间的路径所呈现的约束状态而非Slack(时序裕量)的恶化程度

本章演示了如何利用 Vivado® 工具并使用 PL AXI GPIO 来创建嵌入式设计。其中还演示了如何在 Versal 器件上为基于 Arm® Cortex™-A72 核的 APU 配置并构建 Linux 操作系统。

在VCS中,一个仿真会话可以保存在一个Tcl文件中,以后可以加载。当我从Vivado调用VCS时,如何加载一个保存的会话?

本章用于演示如何为 Versal™ ACAP 集成和加载引导加载程序、裸机应用(针对 APU/RPU)和 Linux 操作系统。

在Ubuntu系统中,当试图在内核代码中设置断点的加速应用程序上运行仿真调试时,工具不会在断点上停止,而只会在主机代码断点上停止。

PetaLinux基于Yocto,编译Linux内核、文件系统等,非常庞大,需要的软件很多。如果从网络下载,可能消耗比较长的时间。本文基于Xilinx PetaLinux 2020.2.

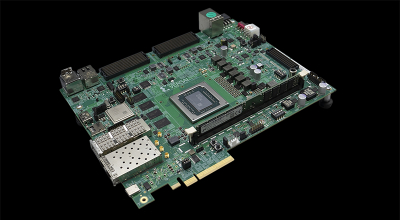

本文提供了一个基于VCK190 ES1开发板和2021.1 Vivado/Vitis的例子,用来简单介绍在Versal里实现数据从PL 经过 FPD CCI 到达 NoC DDR的一致性传输。

本文主要讲述了如何避免FSM输出毛刺。