ZU1 MPSoC:小巧、强大、现已上市

judy 在 周四, 04/21/2022 - 17:00 提交

如果您正开发一款智能边缘应用,需要将处理能力融于超紧凑的封装中,那么我们要告诉您一个好消息:Zynq® UltraScale+™ ZU1 MPSoC 现正以更多样的封装形式出货,包括超紧凑 InFO 封装。

如果您正开发一款智能边缘应用,需要将处理能力融于超紧凑的封装中,那么我们要告诉您一个好消息:Zynq® UltraScale+™ ZU1 MPSoC 现正以更多样的封装形式出货,包括超紧凑 InFO 封装。

我在一个自定义平台上运行我的项目,而我的目标平台的Vivado项目在Vivado合成中使用了以下额外选项。当我运行Vitis链接器时,我看到以下错误。

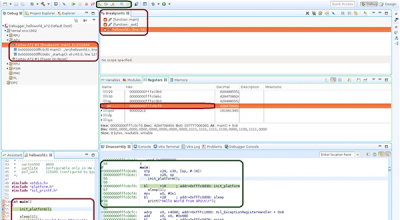

本章描述了对您所执行的设计流程可能出现的各种问题进行调试的方法。

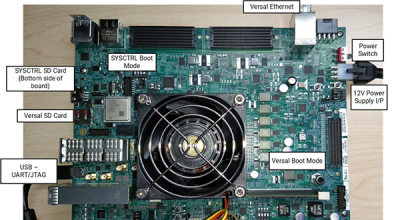

我们早已迫不及待,此刻终于可以正式发布搭载 AI 引擎的 Versal Premium 系列。新一代无线系统要求高性能信号处理,并能够处理进出计算器件的海量数据。

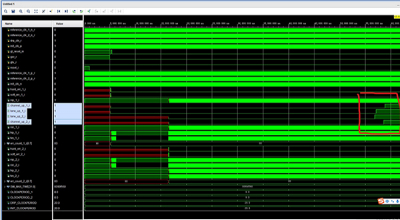

本文描述了如何在设计的早期阶段使用 Xilinx® Power Estimator (XPE) 工具进行功率分析。

赛事以培养学生从算法到硬件加速的能力为主,除了万元奖励外,参赛同学将获得与学术界、产业界广泛交流的机会。

Xilinx的技术生态做的非常好,基本上所有常用的IP核都有官方例程供开发者学习,咱不用白不用,今儿咱就一起白嫖他一手----从官方例程开始学习如何具体使用这个IP核。

阅读本文将有助于你的FPGA选型和设计过程,并且有助于你规避许多难题。

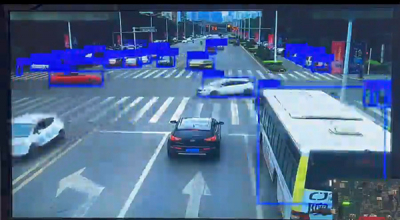

Avnet Smart Model Select 应用是一个示例设计,它演示了如何将 Vitis 视频分析 SDK 示例设计 作为 Kria 加速应用部署至 KV260 视觉 AI 入门套件。