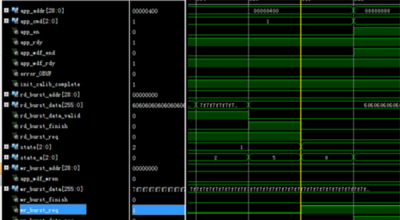

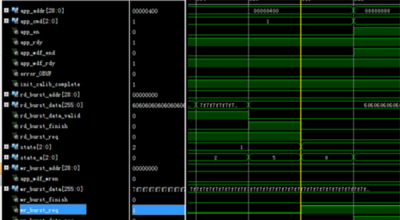

DDR3读写时序

judy 在 周一, 03/14/2022 - 09:26 提交

DDR接口信号分为DDR对外接口信号、用户应用接口信号和读写控制信号。对外接口信号直接与DDR芯片连接,用户应用接口信号为DDR控制器IP输出信号

DDR接口信号分为DDR对外接口信号、用户应用接口信号和读写控制信号。对外接口信号直接与DDR芯片连接,用户应用接口信号为DDR控制器IP输出信号

本文描述了针对Versal® ACAP的PID控制器设计与模型合成器。

Vitis视觉库是一个FPGA加速视觉功能的集合,类似于OpenCV中的功能。虽然这些内核的实现并不依赖于OpenCV,但许多视觉库的功能都提供了示例设计测试平台,使用OpenCV来演示加速内核的功能。

最近几天读了Xilinx网站上一个很有意思的白皮书,名字叫《Get Smart About Reset:Think Local, Not Global》,在此分享一下心得,包括以前设计中很少注意到的一些细节

本文说明了在Xilinx® Versal® AI Core器件上实现任意重采样的情况,其中控制器在可编程逻辑中,而繁重的计算被映射到AI引擎中。

在本文中,我们以vivado自带综合器为例、以verilog为编程语言,看看如何理解和利用警告信息排除代码中的小bug。

本文章探讨一下FPGA的时序约束步骤

本文将把Xilinx的MIG IP核DDR3的Native接口进行二次封装,将其封装成一个类似FIFO的接口,使其应用起来更加方便简单。

AMD/Xilinx 发布了其 VCK5000 AI 推理卡的改进版本以及一系列直接针对 Nvidia 的 GPU 产品线的竞争性基准测试。AMD 表示,新的 VCK5000 的性能是早期版本的 3 倍,并且 TCO 是 NvidiaT4 的 2 倍。

为了便于修改Linux kernel代码,使用下面命令对Linux kernel代码进行格式重排。