基于Vitis JESD204B官方IP核的调试

judy 在 周二, 02/22/2022 - 16:36 提交

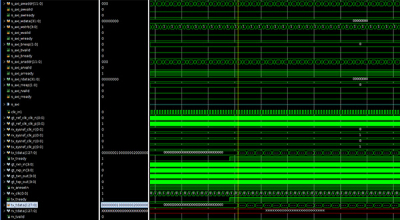

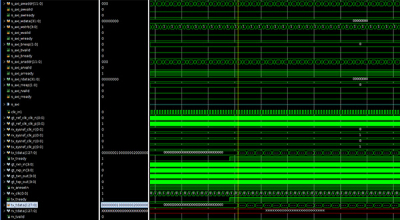

系统主要采用官方JESD_PHY(免费),JESD_RX(评估版),JESD_TX(评估版)三个IP核做测试,采用自发自收,外部GT引脚回环方式。其中,PHY采用4个LANE接收和发送数据,一般线速率为参考时钟的40倍

系统主要采用官方JESD_PHY(免费),JESD_RX(评估版),JESD_TX(评估版)三个IP核做测试,采用自发自收,外部GT引脚回环方式。其中,PHY采用4个LANE接收和发送数据,一般线速率为参考时钟的40倍

2021赛灵思自适应计算挑战赛答疑会1-4集锦

DDR3 SDRAM 简称 DDR3,是当今较为常见的一种储存器,在计算机及嵌入式产品中得到广泛应用, 特别是应用在涉及到大量数据交互的场合

根据ABI Research的最新报告指出,直至2027年,机器视觉(Machine Vision)将成为汽车、医疗保健、制造、零售、智能建筑、智慧城市、交通与物流等主要市场,数字化和自动化的关键支持技术。预计将达到360亿美元市场规模

训练好的模型在部署过程中的Vitis AI转换过程要经过优化、量化和编译等步骤。尤其是量化,可以通过三种不同的方式实现。

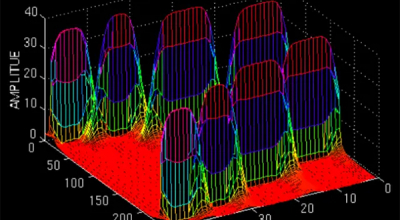

从傅里叶变换到小波变换,并不是一个抽象的东西,完全可以讲得很形象。小波变换有着明确的物理意义,如果我们从它的提出时所面对的问题看起,可以整理出非常清晰的思路

时钟信号在很大程度上决定了整个设计的性能和可靠性,尽量避免使用FPGA内部逻辑产生的时钟,因为它很容易导致功能或时序出现问题

本文提供有关使用 Zynq® UltraScale+™ MPSoC 的产品的 FIPS 140-3 认证的入门知识。

本文将指导用户,如何使用第二种方式产生的例子工程,添加自己的数据激励,用于完成自己所需要的仿真验证

BEL是最底层的基本元素,也可以叫atomic unit(原子单位),BEL是FPGA中最小、不可分割的组件。BEL有两种:Logic BEL和Routing BEL。