论一位女工程师的自我修养

judy 在 周三, 08/05/2020 - 10:29 提交

本期AI观察室,让我们走近赛灵思AI算法总监田露,走进一个女工程师的世界,了解一个她和她所代表的女工程师的实践与思考。。

本期AI观察室,让我们走近赛灵思AI算法总监田露,走进一个女工程师的世界,了解一个她和她所代表的女工程师的实践与思考。。

智能网联是汽车行业发展最重要的趋势之一,包括自动驾驶和车联网两个主流方向。各国政府包括中国政府在内,都在积极地制定智能网联技术路线并不断完善本国的智能网联标准体系。不可否认,智能网联技术及其标准体系都将对汽车座舱发展产生深远的影响。

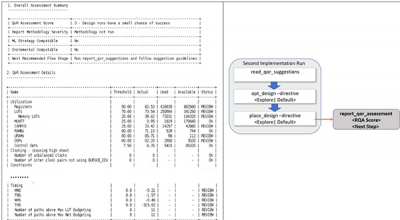

通过之前的博文,我们已经学会了如何使用 Report QoR Assessment (RQA) 和 Report QoR Suggestions (RQS) 来改进总体设计分析以及设计的时序收敛体验。本篇博文将通过一个具体设计示例来演示如何在实现流程中将 RQA 与 RQS 结合使用。

首届赛灵思自适应计算挑战赛(Xilinx Adaptive Computing Challenge)继续火热报名中!为了帮助国内开发者更好更快地报名成功,Xilinx技术社区帮您简化流程,手把手教您如何报名开发者比赛,赢万元大奖!

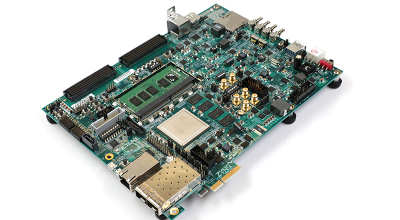

随着新一代网络被部署用来支持日益多样化的高带宽应用组合,网络供应商和数据中心运营商需要快速扩展数据包处理能力,同时最大限度地降低资本支出/运营成本,并保持灵活性,从而适应未来的连接标准。为满足未来的不同需求,赛灵思推出了Kintex UltraScale+ KU19P FPGA。

赛灵思今日宣布加入 Open RAN 政策联盟,致力于为Open RAN 5G 技术的开发和部署提供有力支持。Open RAN 政策联盟的成员提倡将 Open RAN 作为首选解决方案,提高多厂商生态系统的互操作性和安全性。

MicroBlaze可以使用AXI BRAM存放数据和指令。有些客户软件很大,需要把AXI BRAM的空间做到最大。AXI BRAM底层是Block RAM或者Ultra RAM。器件的Block RAM或者Ultra RAM个数,决定了AXI BRAM的大小。在ZCU106单板上,有312个Block RAM,有96个Ultra RAM。客户需要1MB存储空间。

Vitis™ AI 开发环境是 Xilinx 的开发平台,适用于在 Xilinx 硬件平台(包括边缘器件和 Alveo 卡)上进行人工智能推断。它由优化的 IP、工具、库、模型和示例设计组成。Vitis AI 以高效易用为设计理念,可在 Xilinx FPGA 和 ACAP 上充分发挥人工智能加速的潜力

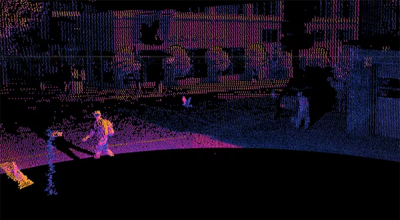

近日,赛灵思公司与美国 Quester 公司联手推出一款可扩展数字化多光束快闪激光雷达。一石激起千层浪,包括机器人和自动驾驶出租车在内的 15 个不同市场均将从此收益,交通行业也将因此迈上发展新台阶。