开发者分享 | 远程共享和访问赛灵思器件

judy 在 周一, 07/20/2020 - 14:13 提交

在某些情况下,比如远程工作时,可能需要访问本地不可得的器件。本篇简介教程演示了如何共享并访问位于远程实验室内的开发板或归同事所有的开发板。

在某些情况下,比如远程工作时,可能需要访问本地不可得的器件。本篇简介教程演示了如何共享并访问位于远程实验室内的开发板或归同事所有的开发板。

Vitis™ AI 开发环境是 Xilinx 的开发平台,适用于在 Xilinx 硬件平台(包括边缘器件和 Alveo 卡)上进行人工智能推断。它由优化的 IP、工具、库、模型和示例设计组成。Vitis AI 以高效易用为设计理念,可在 Xilinx FPGA 和 ACAP 上充分发挥人工智能加速的潜力。

在上篇文章中了整理了一些针对开发者参加本次挑战赛的常见问题并解答,本期文章将对初创企业参赛的一些常见问题整理并解答。

此次“自适应计算挑战赛”面向所有独立开发者和初创企业。比赛要求使用 Vitis / Vitis AI 在 Xilinx 平台上实现算法和应用的硬件加速。获奖者将获得奖金! 立即注册并开始设计吧!

现代 RF 信号链对于跨多通道的数据转换器性能具有极高的要求。换言之,对于赛灵思 RF Data Converter 而言,关键要求之一是在多个 ADC/DAC Tile、RFSoC 器件甚至开发板之间都必须保持同步。了解赛灵思如何探索多块同步 (Multi-Tile Synchronization) 问题解决之道

赛灵思与Hackster.io携手推出的首届赛灵思自适应计算挑战赛现已拉开序幕。赛灵思诚邀独立开发者和初创企业参赛,借助Vitis™ 统一软件平台和 Vitis AI 发挥杰出才能,为加速工作负载开发创意设计解决方案。两项竞赛的报名已于 2020 年 7 月 7 日正式启动。以下是本次竞赛的参赛指南

近期,在推动 IT 基础设施向异构计算转型的过程中,赛灵思与 VMware 展开协作,在 VMware 的云计算虚拟化平台vSphere上测试 FPGA 加速。由于赛灵思 FPGA 越来越广泛地应用于 ML 推断加速,本文将展示的是如何将赛灵思 FPGA 与 VMware vSphere 相结合,在虚拟部署和裸机部署上实现基本相同的高吞吐量、低时延 ML 推断性能。

Xilinx 隆重推出自适应计算挑战赛!比赛要求开发者和初创企业使用 Vitis™ / Vitis™ AI 在 Xilinx 平台上实现算法和应用的硬件加速。开发者冠军将获得 1 万美元奖金,初创企业冠军将获得 10 万美元奖金!

基于新型的赛灵思实时服务器( Xilinx RT Server)参考架构,两大全新一体机将双管齐下,助力当今服务提供商以每通道最低成本提供视频质量和比特率优化的多种类型应用。本文我们将开始为您揭开这一与众不同的实时转码一体机...

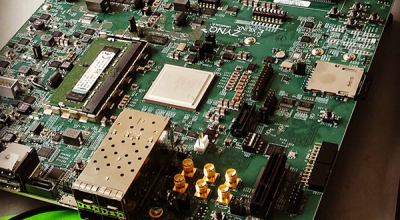

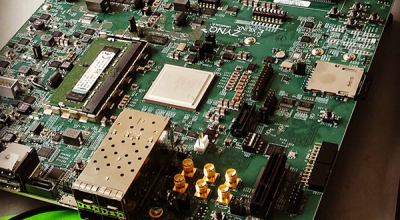

本篇博文将为您演示如何创建 AXI CDMA Linux 用户空间示例应用。示例设计将在 Zynq UltraScale+ RFSoC ZCU111 评估板上实现通过 AXI CDMA 把数据从 PS DDR 传输至 AXI BRAM。