采用 Vitis 技术的 Ultra96 (v1):DPU 集成与 MIPI 平台教程

judy 在 周三, 06/10/2020 - 17:48 提交

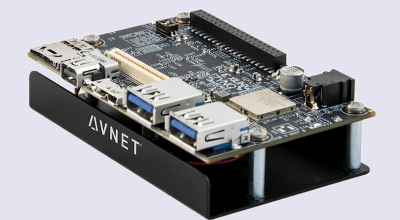

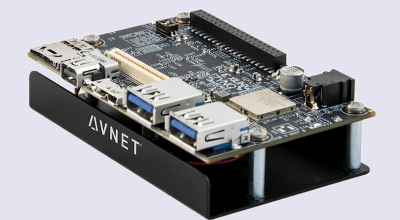

Ultra 96™ 是构建边缘用例机器学习应用的绝佳平台。Zynq® MPSoC ZU3 器件采用的 96 电路板的外形尺寸以及可编程逻辑,使其能够灵活地添加用于此类终端应用视频输入的通用 MIPI CSI2 RX 标准接口。同时为了驱动高性能、低功耗机器学习边缘应用,也可以将赛灵思深度学习处理单元 ( DPU ) 集成到设计中。

Ultra 96™ 是构建边缘用例机器学习应用的绝佳平台。Zynq® MPSoC ZU3 器件采用的 96 电路板的外形尺寸以及可编程逻辑,使其能够灵活地添加用于此类终端应用视频输入的通用 MIPI CSI2 RX 标准接口。同时为了驱动高性能、低功耗机器学习边缘应用,也可以将赛灵思深度学习处理单元 ( DPU ) 集成到设计中。

本指南为 Zynq-7000 AP SoC、Zynq® Ultrascale+™ MPSoC 和 MicroBlaze™ 器件在 Xilinx® 虚拟仿真平台 (QEMU) 上进行软件开发提供了全面的指导。包括入门和快速参考信息,以及如何调试和创建QEMU启动映像的信息。

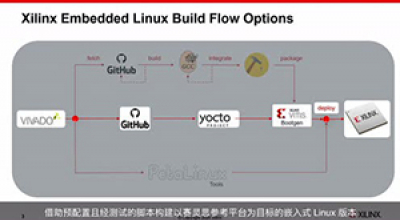

在本视频中我们将简单介绍 PetaLinux 工具开发与构建环境此环境支持客户构建以赛灵思器件为目标的 Linux 版本,并快速评估赛灵思嵌入式平台。

赛灵思今日以线上会议形式举行了主题为“创‘新’正当‘适’”的大中华区核心市场中国媒体沟通会。在会上,赛灵思大中华区销售副总裁唐晓蕾阐述了赛灵思对数据作为“新基建”核心的洞察,分析了数据万有引力作用下,“新基建”七大核心领域从云到边缘智能计算的机遇与挑战,以及赛灵思所引领的自适应计算与“新基建”的完美契合和光明前景

疫情肆虐,全球经济全面遭受重创且持续低迷。然而,近日中国自动驾驶领域、嵌入式人工智能自动驾驶先锋企业魔视智能,Motovis (赛灵思在中国自动驾驶领域的重要合作伙伴之一),却逆势迎来 A2 轮融资成功的利好消息,融资金额高达一亿元人民币!

本文介绍如何利用赛灵思 Alveo 卡实现应用加速的简介,包括阐述基本架构方法、识别适用于加速的代码以及利用软件 API 以最有效的方式来管理存储器并充分发挥 Alveo 卡的强大作用。

说在前面,本文分享了两个视频,从 DFX 的布局规划,再到布局规划的进阶。两个视频,20分钟帮您快速掌握 DFX 的布局规划...

随着赛灵思 Alveo 自适应计算加速卡的发布,数据中心各种工作负载开启了自适应计算加速的历程。本期小编特整理了有关 Alveo 的一批中文文档,以供各位随时下载和查阅。

本次网络研讨会描述了两个使用 Zynq UltraScale + RFSoC 进行无线通信的设计示例。 首先,让我们回顾一下针对大规模 MIMO(64x64),100MHz LTE(ORAN 7.2 split)的设计,并解释其实现和选型性能数据。

在数据指数级增长对智能化、灵活应变的网络和数据中心解决方案提出极高要求的今天,全新 Virtex UltraScale+ VU23P FPGA 为行业提供了所需的最大吞吐量、强大的数据处理能力以及灵活性优势,使其可以适应不断演进发展的连接标准,并满足当前与未来需求