作者: Austin Lesea,文章来源:复及科技

编者按:

长期以来,人们对用FPGA实现的创新大张旗鼓,对里面使用的FPGA保持秘而不宣。

号称对专利最为开放的马斯克,旗下Starlink卫星中的星载FPGA平台,网上公开的信息寥寥,更趋封闭保守之势。

据说在赛灵思芯片应用开发过程中,调试验证方面就曾遇到大麻烦。

不管是利用FPGA的硬件仿真功能,加速IC设计左移;或者在终端市场上用于制造产品,直接来自厂商的技术支持非常重要,其对器件底层技术细节足够了解,拥有芯片的关键Know-How。

在IC设计行业,有调试是硅前验证“最后一公里”之说。

在垂直细分市场,当形容FPGA应用开发的高质量时,也常奉上“设计团队在这款芯片上实现的性能,厂商专家认为已经是器件本身的极限”的溢美之词。

或者是“在航天应用中之所以能够使用商用级FPGA(Commercial COTS),得益于对辐射效应的理解,以及在FPGA设计、板卡级的最佳缓解策略实现”等等。

EDA硬件辅助验证行业,一直代表了FPGA最先进的调试水平,在某种程度上,也引领了验证技术发展趋势。

其中,IC物理原型验证服务稳居第一的新思科技,2011年时联合龙头厂商赛灵思,共同出版了“原型设计的最佳实践”一书。

由芯片厂商的首席工程师亲自捉刀,负责撰写基于FPGA的原型设计、芯片硬件和调试软件概述。

虽然本文以采用40nm工艺的第六代Virtex,容量最大的LX760为对象,重点介绍当时FPGA结构,但涉及的调试验证工具和方法,具有普适性。

包括与软件调试类似的设置硬件断点、单步功能,以及快速便捷获取信号的可见性等,对所有FPGA用户不但具有通用价值,至今仍很先进。

特别是对于28nm工艺的FPGA,以及后续更先进芯片器件,更具实用价值。

芯片规模越大,应用开发更为复杂,就越需要。

以下为正文:

FPGA的强大不仅取决于芯片自身的功能,也与相关EDA工具的支持和使用密不可分。

FPGA概览

FPGA芯片是IC物理原型设计的基座,SoC设计的最终实现平台。

经过多年发展,作为异构架构的超大规模逻辑阵列,以令人印象深刻的时钟速率运行,FPGA芯片的进步,与整个半导体技术的发展步调一致。

而且随着架构的持续改进和工艺技术的发展,芯片容量保持急剧增长,并完美契合摩尔定律发展路线。

在部分架构中使用3D IC技术,使得FPGA更是超越摩尔定律。

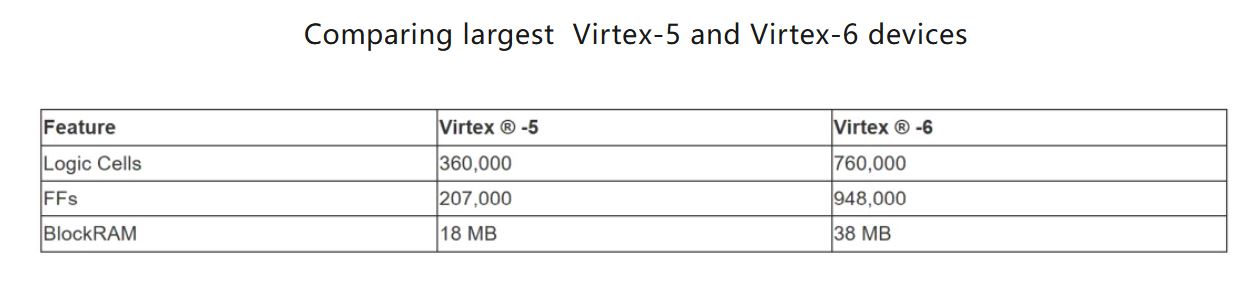

目前赛灵思最新的第六代高性能Virtex FPGA系列,由Virtex-5架构演变而来,具有增强的功能、更大的容量、更高的性能和更低的功耗。

与上一代容量最大的LX330相比,Virtex-6 LX760的逻辑资源(LCs)增加了一倍以上、触发器(FFs)更是增大近5倍,可以更好地支持流水线设计。

让我们花一些时间,从基本逻辑块开始,以及每个模块对基于FPGA的原型设计任务的作用,先大致了解FPGA技术。器件和相关结构的完整细节,可通过本书附录中的参考书目和相关资料,进一步查阅。

Configurable Logic Blocks

可配置逻辑块CLB

CLB是硬件设计必不可少的构建模块,由两个Slice组合而成,以阵列的形式排列在芯片内部,通过互连资源相互连接,并与其他类型的资源连接。

设计中的时序和组合逻辑,由CLB中的Slice实现,包含查找表(LUT)、存储单元(DFF)和附加的级联逻辑等。

典型的4输入LUT的核心是16×1 RAM,用于创建一个包含四个输入和一个输出的逻辑函数,也就是“命令”16位RAM模拟一个逻辑功能。

事实上,我们可以把16位RAM看作早先的卡诺图,这也是编程的一种方式。因此奇偶校验、异或、与、或等逻辑函数,可以有效打包到最少数量的lut中,用于执行所需功能。

lut并不是一个独立单元,而是被嵌入到其他结构中,包括FF、进位链、算法、存储器和其他复杂结构。

算术函数也可以放在lut中,并且在器件中也有硬连线的预进位逻辑,性能可能比单独使用lut得到改善。

Virtex-6中包含6输入LUT(即64位RAM),用于实现六输入的函数生成器,可以实现任意定义的布尔函数。通过综合工具编程,根据需要从硬件编程语言编写的设计中创建LUT内容。

最后在器件下载配置完成后加载LUT RAM,从64位RAM创建一个复杂的6输入功能。

LUT memory and block memory

LUT存储器和块存储器

块存储器资源(BRAM)对于较小的内存非常有用,是FPGA中第二重要的资源。可以选择从小型寄存器文件、移位寄存器到大规模ram的存储器类型。

作为主要的构建模块,BRAM可以组合使用,用来模拟更深或更宽的存储器。这通常由综合工具执行,自动判断,将较大的内存划分到多个BRAM中。

面向流片的IC物理原型设计,包括多种不同类型的存储器,例如RAM、ROM、内容可寻址。在绝大多数情况下,这些存储器从单元库或内存生成器程序实例化得到。

需要FPGA能够尽可能高效地表示这些存储器,通常需要专用工具来实现这一转换过程。

但常规FPGA应用开发和产品原型,不需要考虑这样的转换问题。

DSP resources

DSP资源

对于设计中包含的算术功能,如乘法器、累加器和其他DSP逻辑,FPGA通过提供有限数量的专用DSP块来满足这些需求。

在Virtex-6系列中被称为DSP48E1块。

这些专用的、可配置的、低功耗的DSP Slice,结合了高速度和小尺寸,同时保留了系统设计的灵活性。

除了可以通过DSP Core 实例化进行模式配置之外,大多数特征都是由综合工具自动推断出来的。

Clocking resources

时钟资源

常规FPGA应用开发和IC物理原型设计,时钟资源和时钟网络是两者之间的主要区别。

后者几乎可以完全自由地指定尽可能多的时钟网络,但在FPGA中可以实现多少时钟网络,则是有实际使用限制的。

如果IC设计团队未能有效将时钟映射到FPGA时钟资源,可能会导致重大的项目延迟。

但FPGA应用开发,通常不需要考虑这样的时钟映射问题。

时钟资源可分为时钟生成和时钟分配:

时钟生成

由时钟管理块CMT的可配置单元中生成,在Virtex-6 FPGA中,包括两个混合模式时钟管理器(MMCM)。

这是一种基于锁相环(PLL)架构的多输出频率合成器,具有增强的功能和能力。CMT中的每个MMCM都可以单独处理。

时钟生成作为FPGA中的关键模块,许多时钟特性不能交由综合工具自动推断,必须实例化到RTL的FPGA版本中。

时钟分布

几十年来,器件厂商一直在努力生产具有尽可能多时钟的器件,同时又不浪费面积资源。因此,FPGA非常适合实现有限数量时钟网络的常规同步电路。

为了提高效率,在大多数芯片中提供了不同时钟资源的层次结构,从全局低倾斜时钟到本地低扇出时钟。并且,确保时钟资源的良好使用是综合工具和布局布线工具的任务,但有时可能也需要人工干预。

在Virtex-6中提供五种不同类型的时钟线,以满足高扇出、低传播延迟的不同时钟要求,并实现跨芯片的低倾斜。

时钟分布资源通常由由综合工具自动推断,但如果需要区域时钟,则通常需要设置位置约束,以便将时钟负载与特定区域关联起来。

input and output

输入输出

在Virtex-6器件中,每个I/O引脚都是可配置的,可以符合多种I/O标准,最高使用2.5V。除了供应引脚和一些专用配置引脚外,所有其他封装引脚都具有相同的I/O功能,仅受某些Bank/分组规则的限制。

I/O是设计RTL设计顶层IO,以及FPGA间连接的主要构建块。默认的单端I/Os和DDR I/Os会被自动推断出来。

通过综合工具读取约束管理器中的属性,分配选择不同的I/O类型,然后传递给布局布线工具。iodelay和I/O SERDES则只能通过Core实例化来包含。

Gigabit transceivers

高速收发器

越来越常见的是高速串行通信通道,在ASIC和SoC设计的硅前验证、即IC的芯片物理原型阶段,用于通过背板或设计之间的长距离信号收发。

在RTL设计中,它们总是作为黑盒实例化,并引用最终芯片布局中的物理I/O。我们将在后面的章节中看到如何在基于FPGA原型中处理这个问题。

要在FPGA中对这些超高速串行收发器进行建模,需要专门的片上电路,包括能够处理高数据速率下信号完整性问题的差分I/O。

反过来,接收器基本上是一个串行转换器,将输入的位串行差分信号转换成并行的字流,每个字的宽度为8、10、16、20、32或40位。接收器接收输入的差分数据流,通过可编程均衡器(补偿PC板和其他互连特性)将其馈送,并使用FREF输入,初始化时钟识别过程。

GTX虽然是一个非常强大的功能,但由于它们的复杂性和可配置选项,不会被综合工具自动推断出来,但可以通过对Core进行实例化来添加。

Virtex-6系列每个都有8到36个(GTX)电路,但LX760 除外,该芯片不具有GTX功能。

Ethernet, PCI Express®, CPU etc

内置IP

FPGA在实现媒体访问控制器(MAC)和物理接口收发器(PHY)的标准接口方面变得越来越有能力。

如果选择的FPGA具有内置的这些功能,那么这些可以用来替代那些最终将嵌入到SoC中,但可能在RTL中显示为黑盒的物理IP块。

在Virtex-6 FPGA中,PCIe和以太网MAC和PHY已被集成到芯片内部。

一些芯片内部还包括CPU硬核,通常是某种类型的ARM IP核。这些IP核针对FPGA进行了优化,并且在综合到FPGA时,将以比等效SoC的RTL(软核CPU)高得多的速度运行,通常可快十倍。

此外,当今大多数SoC设计都运行多个CPU内核,通常具有不同的功能或配置。

虽然内置IP功能强大,但硬IP模块不会被综合工具自动推断出来,需要通过IP核的实例化来完成。

System monitor

系统监控

FPGA内置监视器对于避免因错误操作而造成器件损坏至关重要。

如果高速运行的硬件设计未能按预期执行,或者受到错误的影响,将引起功耗,温度,电压的异常。

每个Virtex-6 FPGA包含一个系统监控电路,提供温度和电压信息。

默认情况下,系统监视器对片内ADC传感器输出进行连续采样。最新的测量结果以及最大和最小读数存储在专用寄存器中,以便随时通过DRP或JTAG接口访问。

报警限制可以自动指示温度过高或者电压超限,启动掉电保护。

系统监视器不需要在设计中进行显式实例化。

一旦建立了适当的电源连接,就可以通过JTAG测试访问端口(TAP)随时访问测量数据,甚至可以在配置之前或断电期间访问。

这个模块主要是一个“管理”监视器,通常在实际设计之外,通常通过JTAG链读取设备和系统的健康状况。如有需要,也可以通过实例化来包含片内ADC传感器。

截至目前,我们已经看到综合工具的任务是将设计映射到可用的FPGA资源中。自动化程度越高,构建FPGA原型的过程就越容易越快速。

IC物理原型设计的三大原则

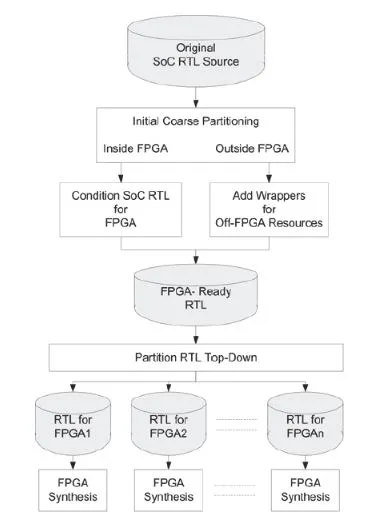

对于原型设计流程中的"综合、FPGA结构适配、多FPGA设计分割、布局布线"步骤,需要专门考虑原型验证的三种特殊情况。

Law 1: 芯片设计规模可能比单个FPGA更大

此时,需要将设计划分为到多个FPGA芯片上进行调试验证。这是EDA硬件辅助验证行业特有的Partioning技术,即通过图划分将多块FPGA“拼接”为严丝合缝的统一硬件平台。

随着单个FPGA的硬件容量变得更大,由1块FPGA、2-4块FPGAs提供的原型验证服务,已经能满足70%以上的IC设计需要。

Partitioning Flow

用户可以在RTL源码或者综合后的网表级别,按需手动划分;也可以使用服务供应商的EDA工具,对设计进行自动分割,如新思科技的Certify等。

Law 2: 芯片设计的运行速度比FPGA快

前者的速度由时钟资源和硬连线决定,频率可以高达数GHz。

而FPGA芯片有限的时钟资源、大量布线带来的时间开销,就算速度最快的单FPGA,运行速度也只是在数百MHz左右。

对于由多FPGA构成的原型平台,除了时钟资源限制,有限数量的IO引脚通常是比设备容量或单FPGA性能更大的主要限制因素。

EDA硬件辅助验证行业特有的管脚时分复用技术,将不同的信号多路复用到同一条线路上,在芯片之间传递同步信号,进一步降低了“拼接”而成硬件平台的运行速度。

单FPGA的性能自然是最快的,用户不需要考虑针对超大规模IC才会使用的诸多专有技术。

Law 3: 芯片设计代码并非直接映射到FPGA上

IC设计的代码需要作相应的改动,才能适配到FPGA硬件平台。

所以在IC设计行业,将设计部署到FPGA上进行原型验证,根据复杂程度和供应商的配套工具表现,用户需要少则几天,长达数周以上的Bring-up过程。

除了多FPGA的设计分割,另一个耗时的任务就是RTL Modification,即代码适配。需要将IC设计源码中定义的时钟资源、存储资源等,进行相应的转换适配,才能高效映射到FPGA芯片上。

综合工具在很大程度上,就是用自动化能力帮助用户更好应对“原型设计三定律”:

1) 将设计划分到多个FPGA上运行,需要进行分割Partitioning;

2) 在多FPGAs上尽量减少性能损失,需要对管脚进行时分复用TDM;

3) 对设计进行的相应改动,才能适配FPGA结构。

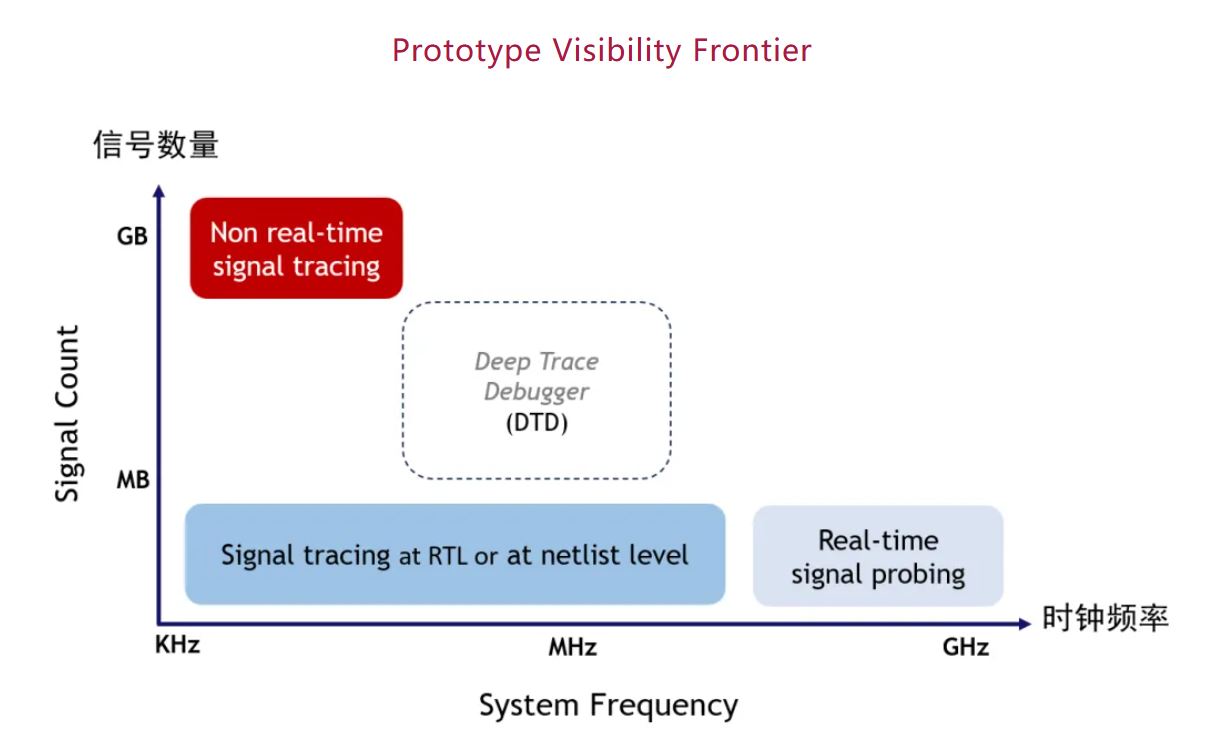

所以在性能(Speed)、设计容量(Capacity)和调试可见性(Debugging&Full Visibility)方面,具有不可兼得三角关系。

硬件容量越大,多片FPGAs协同工作的运行速度越慢,调试难度相应也就越大。

简单来说,针对超大规模IC设计的三大专有技术,分别对应设计分割、管脚时分复用、RTL代码适配等,也是EDA厂商提供原型验证服务的三个收费点,或者说最大的服务价值。

如果在设计可以在一块FPGA上完成,就只需RTL代码移植和适配,遵从第三个原则即可。

对于FPGA应用设计,三大原则都不存在。

但调试是所有用户的刚性需求。

调试方法及工具

信号可见性或者可观测能力必不可少,一般通过探针访问设计的内部节点、设置事件触发器等方式获取。

由FPGA厂商提供的现有调试手段,通常是在让用户在设计中增加一些捕获逻辑,用于根据可编程事件将选定的信号抓取到芯片内部未使用的BRAM中,接着在捕获完成后,再使用JTAG从FPGA读出信号。

可以用多种方式查看,例如通过波形或直接在源代码中显示信号值。

用户可以在综合之前,在RTL中实例化捕获逻辑;也可以在综合后网表级别植入捕获逻辑,使RTL保持完整。

此外,一些工具还允许快速修改FPGA配置,而无需经历通常冗长的布局布线过程。

Design instrumentation for probing and tracing

在设计中植入探针

在设计启动过程中,如果不能正常工作,需要进行状态诊断,并了解其行为。即使设计初始化完成,成功启动,在运行过程中,也可能出现非预期的行为。

在这两种情况下,FPGA和其他组件I/O引脚提供的可见性,可能不足以应对这种情况。

在FPGA中实现的内部信号探测技术分为两大类:实时信号探测和非实时跟踪捕获。

以下是用于提升调试效率的技术和工具介绍:

Real-time signal probing: embedded test points

实时信号探测:嵌入测试点

实时信号查看是最简单的探测设计内部节点的方法。用户直接修改设计,并将内部节点引出到FPGA管脚,实时查看(Add test points to RTL)。

设计中的待观测信号,使用逻辑分析仪或示波器进行设计分析。

除了信号探测,还可以用于发现竞争条件和意外的“小”信号(“runt” signals)。

这种方法的优点是只需要很少的路由和逻辑资源,甚至可能不需要消耗逻辑资源。

缺点是用户想查看不同信号或一组信号时,必须进行RTL更改,重新经历综合和布局布线过程。

另一种可快速修改RTL设计的方法,是直接使用赛灵思FPGA Editor。

该工具可直接在网表级别进行设计编辑和修改,用户可以添加设计元素,如引脚,并将它们连接到需要探测的节点。

需要注意的是,尽管FPGA Editor工具非常强大,但使用起来也很复杂。因此,通常只有专家级工程师才会使用到这个编辑器工具。

就像生物医药领域的“基因剪刀手”一样使用,可对电路节点进行精细控制和修改。

Real-time signal probing: non-embedded debug port

实时信号探测:非嵌入式测试点

有专用的EDA工具,例如Synopsys的CHIPit系统。从每个FPGA保留固定数量的引脚,并将它们路由到电路板上的探测点,作为调试端口,外接逻辑分析仪。

用户可以使用按层次展开的设计信号列表,选择待观测的目标信号。然后再通过工具自动调用FPGA Editor,直接修改布局布线后的网表,将目标信号连接到探测点。

缺点是有可能使用的不是最佳互连资源,优点是不需要重新编译,即无需综合、布局布线过程,从FPGA内部逻辑到调试端口的连接只需要很短的时间。

能够快速提取信号并在示波器上观察,在调试过程中也是非常有用的。

Non real-time signal tracing

非实时信号跟踪技术

直接使用外接示波器、逻辑分析仪器进行FPGA信号观测,采样速度最快,但需要更改RTL并进行重编译;FPGA Editor没有硬件重新编译过程,但使用门槛高。

两种方式可用于探测的引脚数量有限。

但非实时信号跟踪,由于使用了不同的探测机制,绕过了以上两大限制,是前者的强力补充。

没有硬件重编译过程,可以读取任意信号值。

可以直接使用赛灵思FPGA芯片的“回读”特性(Readback),也有相应的EDA工具。

后者由调试软件和辅助硬件两部分共同组成,对FPGA内部进行信号捕获。辅助硬件位于FPGA内部,并事先添加到设计模块中,用于监控和捕获用户选择的一组信号。

先在调试软件中设置触发条件和信号捕获类型,再由辅助硬件利用FPGA芯片的“回读”特性,通过JTAG端口读取设计中的所有寄存器(FF)的值,以及BRAM数据。

最后,使用JTAG配置下载线缆,将捕获的信号数据从FPGA内部捕获缓冲区传输到主机上。

这些数据既可以在调试软件中观测,也可以通过其他波形显示工具查看。

也可利用赛灵思的快速并行配置接口SelectMap等更快配置通道,如Synopsys的CHIPit调试工具,就使用SelectMap通道,对寄存器数据快速回读捕获。

非实时信号跟踪技术和工具,对于单FPGA调试,非常有用。

These tools are extremely useful for an individual FPGA debug.

除了捕获故障现场数据,用作“事后”分析之外,有些EDA工具还提供“交叉触发”功能,用于与外部测试工具(如信号发生器、软件调试器)进行同步,从而有助于对跨系统捕获数据进行关联。

Signal tracing at netlist level

网表级别的信号跟踪

赛灵思提供的FPGA调试工具,ChipScope的工作原理是在设计中添加额外的探针逻辑,用于通信、触发和跟踪捕获。

植入的探针逻辑与目标设计保持同步,并且与被采样逻辑使用相同的系统时钟,从而避免了采样建立时间和保持时间问题。

需要注意的是,跟踪捕获操作实际上是采样FPGA内部节点上的活动,数据分辨率将仅与捕获时钟相同,所以不能用于信号的时序分析。

不论是将在RTL中直接实例化调试IP Core,还是在综合后网表级别选择需要跟踪的信号,都能进行探针植入。

一旦设计下载到FPGA中,其调试过程是完全相同的。

用户通过JTAG下载电缆与逻辑分析模块通信 ,设置触发条件、捕获模式等。当满足触发和捕获条件时,从FPGA传输捕获的数据,并在主机的软件界面中显示。

Signal tracing at RTL

RTL信号跟踪

新思科技的Identify,其工作方式与ChipScope工具类似,RTL源码中植入探针,而不是像后者那样可以在网表也能植入。

提供信号选择和监视机制,使用户能够更容易地触发跟踪捕获,并将捕获的结果数据与RTL设计进行关联溯源。

Identify由两个子工具组成,RTL植入逻辑(硬件)和RTL调试器(软件):植入逻辑本身的关键部分,称为IICE或智能电路仿真器(Intelligent In-Circuit Emulator),被嵌入到用户的设计中。

IICE包含信号监控逻辑,跟踪捕获和缓冲,以及与主机PC的通信。

跟踪缓冲区通常使用芯片内部一个或多个可用的BRAM。所需BRAM资源的大小取决于要捕获的信号的数量、触发条件以及在更大程度上所需的捕获缓冲区深度。

IICE还包括触发和排序逻辑,用于决定何时进行采样,并通过JTAG与调试软件通信,其中断点和捕获信号的状态在RTL源码中进行高亮显示。

此外,Identify还添加了两个有用的功能,允许我们在设计到达某一行代码时捕获,就像软件工程师调试代码时使用“断点”类似。

另一个是状态注释功能,在使用断点时,使用设计导航工具将信号的状态直接注释到源代码中,用户还可以在源代码行滚动查看采样数据值的变化,大致上类似软件调试工具中的“单步”功能。

调试非常不直观,即使有可见性,也不知道看到的是什么。对于FPGA调试,一直以来工程师普遍抱怨,可见性非常差。

但可见性或者说可观测能力,或者说能够获取尽可能多的数据,是做出正确决策的第一步。

代码是设计出来的,更是调试出来的。

编者后记

随着FPGA规模越来越大,应用设计更趋复杂,同样带来调试验证难度的急剧增加。

2021年,新思科技认为,随着单FPGA硬件规模变得更为可观,调试验证正在超越设计分割、管脚时分复用等专用先进技术,成为EDA厂商新的核心竞争力。

High Debug Productivity is the Prototyping Game Changer

2022年,EDA巨头西门子在IC设计功能验证研究报告中,调试在整个验证过程中已占据近50%的时间。

FPGA应用开发正面临二十年前ASIC设计同样的挑战。

现在28nm主流的FPGA器件,如关键行业用户使用的7K-325T、7V-690T等,曾经也是EDA硬件辅助验证行业十多年前的主要芯片型号。

EDA行业目前最新使用VP1902,单芯片容量高达18.5M LCs,拥有2400亿个巨量晶体管。

同一代的VC1902,容量近2M LCs,从公开的信息看,目前也已进入欧美太空和防务部门的视线,开始进行使用前的测试评估工作。

在更早2008年,使用的还只是Virtex-5 FPGA时,美国航天航空管理局(NASA)启动FVAX(FPGA Verification Accelerator)项目,大量借鉴了EDA行业的调试验证技术。

提升开发质量,加速设计左移。

立足现在,面向未来,拓展EDA硬件辅助验证的服务边界。

复及科技自主开发的forgedaX软件,在计算加速时代,为用户提供经济易用的全新解决方案。

数据可见,设计生产力才能看得见。

可以对所有的FPGA设计进行调试验证。如果是对其它厂商FPGA进行验证,需要用户进行代码迁移部署,就类似简化版的RTL Modification。

比如像空客对包含43块芯片(22个反熔丝高可靠FPGAs,20个ASICs)组成的复杂系统,在赛灵思XCVU440进行验证一样的使用方式。

如果是使用赛灵思芯片进行开发,直接在各类硬件平台上快速部署。

对于关键且重要的行业用户,既有的EDA硬件验证技术远远不够,在FPGA的整个生命周期中,还需要额外考虑功能安全挑战。

是追求绝对可靠的芯片更有保障呢,还是用户在应用层面的设计加固更具性价比?

Tradeoffs in Flight-Design Upset Mitigation in State-of-the-Art FPGAs

我们将介绍Austin Lesea同年发表的专题报告,从赛灵思首席工程师视角,如何高效验证FPGA设计架构的敏感性和脆弱性。