本文转载自: Xilinx技术社区微信公众号

1. 什么是SEU现象

由于高能粒子的撞击,器件的存储单元内容有可能受到干扰,甚至出现翻转。这种单个存储单元的翻转现象(原有内容为0的变成1;或者原有为1的变成了0)就称为SEU (Single Event Upset)。

正常情况下,SEU现象不会导致器件的永久性损坏,并且通过重新配置器件即可纠正。但是如果错误位置位于设计的核心区域,或者错误随逻辑构建的功能模块逐级传递出去,均会导致设计异常

2. Xilinx设计的SEM Core<.strong>

幸运的是,由于SEU现象发生的概率极低,绝大多数普通设计应用并不需要考虑这一问题。但是在航空、航天等高可靠性需求环境下,或者在一些高海拔地区,发生SEU的概率会相应增加。为了及时纠正这种SEU引发功能异常,进一步提高FPGA器件的可靠性,Xilinx开发了Soft Error MitigationCore,简称SEM IP。

FPGA内部的存储单元主要分为4大类:Configuration RAM (CRAM), Block RAM (BRAM), Distributed RAM (DRAM) 以及Flip-Flops(FF)。CRAM用于存储FPGA的配置数据,也是占比最大的存储单元模块。剩下三种的占比依次减少,均可以被用户逻辑使用。

SEM IP可以通过不间断地循环扫描FPGA的CRAM,快速检测出其中是否有存储单元内容和初始值不一致,并且可以把已经被翻转的存储单元的值修复为原来的值。该IP占用资源少,使用方便灵活,可以及时地纠正大多数SEU错误,从而避免了重新配置FPGA的麻烦。

需要注意的是,SEM IP并不会扫描监测剩余三种存储单元。BRAM虽然也是数量较多的存储单元模块,但Xilinx的BRAM可以开启自带的ECC校验功能,纠正SEU或者其他问题导致的数据错误。另外,DRAM和FF的数量相对来说比较少,叠加考虑SEU现象发生的极低概率,这两部分的SEU问题一般可以安全忽略。

3. 入门案例简介

下面我们就基于KCU116开发板,介绍一下如何在设计中加入一个最基本功能的SEM IP,从而开启芯片的SEU检测功能。

1. IP生成

a. 打开Vivado, 基于KCU116建立一个新的空白RTL工程;

b. 选择所使用的FPGA的型号,或者选择所开发板的型号。这里我们选择KCU116,Rev 1.0.

c. 确认器件信息,生成新的工程。

d. 在PROJECT MANAGER的IP Catalog中,选择FPGA Features andDesign-> Soft Error Mitigation -> UltraScale Soft Error Mitigation, 双击打开。

KCU116开发板上是一块XCKU5P-2FFVB676E,对应的IP名称为UltraScale Soft Error Mitigation(3.1)。如果你使用的是其他芯片,那么SEM IP的名称会有所不同,比如7系列的芯片就是Soft Error Mitigation (4.1). 界面和功能会略有不同:

IP的基本默认设置如下图所示:

SEM IP有多种工作模式,设计里面最常用的就是 ‘Mitigationand Testing’。这个模式和其他模式包含的功能如页面中表格所示。Mitigation andTesting 包含了最基本的纠错功能,和验证IP能否正常工作,模拟SEU事件的Error injection功能。此外还支持一些有用的调试命令,比如说读取一些寄存器等等。这里我们就选择这种模式。

Controller Clock Period (ps),是以ps为周期的单位来选择SEM IP工作的时钟。时钟频率越高,纠正错误的速度越快。UltraScale+系列根据型号不同,支持的最高频率可以高达200MHz。考虑KCU116开发板有自带的90MHz的时钟,这里我们选择11111ps。

注意,SEM IP一般要求有独立时钟,即它的工作时钟最好不要同时用来驱动其他逻辑。

其他设置使用默认设置。生成IP。

2. 生成Example Design

SEM IP与其他IP不太一样的地方,是我们建议你完整地把SEM IP的整个参考设计并入用户设计中,而不是仅仅添加一个xci核。参考设计正确地建立了与底层核心硬核ICAP和FRAME_ECC的连接,并且加入了非常有用的一些调试手段,比如VIO,可以观测IP的实时工作状态;比如串口模块,可以方便地实现和IP的交互以及调试。在入门应用或者对于资源没有非常紧张的应用中,直接使用参考设计是最保险的做法。当然,产品中可以把主要针对调试的串口模块去掉。

a. 这里选择右键单击xci文件,选择‘Open IP Example Design

b. 观察Example Design,其包含了IP 的顶层wrapper文件,一些辅助模块(串口,VIO等),以及约束文件以及仿真文件。

c. 为了保证timing的正确,注意保持所有原有的位置以及timing等约束。根据自己PCB的设置,分配一下sem_ultra_0_example_design_impl.xdc里面时钟和串口的管脚。

d. 编译工程,生成用于下载的bit文件。

3. 下载测试

a. 使用micro-USB下载线连接PC和KCU116的JTAG接口,这是为了通过JTAG接口下载配置bit文件。同时使用另外一根micro-USB连接PC和KCU116的USB-UART接口,打开PC上的Tera Term软件,连接Standard COM Port并做如下设置:

b. 通过HW Manager扫描到VU5P器件,下载bit文件。

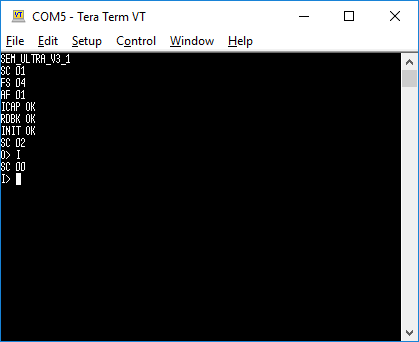

c. 下载成功后,首先可以看到Tera Term上出现了SEM正确初始化的信息:

d. Vivado的Dashboard中,共出现了三个hw_vio_x界面。选中其中的+号,把预先定义好的信号添加进去。

这个界面显示的是IP当前的状态。IP在初始化过程结束后,其status_initialization信号会从高变低,随之进入工作状态status_observation,该信号由低变高。此状态正常应该情况下会看到status_heartbeat信号是一个不断toggle的状态。

这个界面提供了和IP交互的命令行界面。我们这里为了方便,一般把command_strobe,即命令使能信号,做成一个高有效按钮。

一般我们用hw_vio1和hw_vio2就足够了。hw_vio3是用于IP和其他控制逻辑分配资源等的一些控制信号,这里不会用到。

此时的IP已经在正常工作,监测设计的SEU状态了。IP位于哪个状态,那么状态信号status_*就会相应的拉高。

4. 纠错功能验证

如果芯片遭受到了高能粒子轰击并且存储单元出现了内容反转,IP会从observation状态退出,表现为status_observation拉低,status_correction被拉高开始纠错工作。如果纠错成功,IP会重新进入status_observation状态继续工作。由于我们并未开启高级的错误分类功能,所有位置的错误都会被IP认定为是关键位置。因此status_essential信号会被置高并保持不变。

由于真实的SEU事件及其稀少,我们如何能断定IP是否已经正常工作,并且能及时纠正错误呢?SEMIP提供了一个模拟错误注入功能,即Error Injection。下面我们来进行一次单bit注入测试。

a.打开hw_vio2, 由于模拟错误注入需要先把IP切换到IDLE状态,我们需要先在command_code输入E00_0000_0000,然后按一下command_strobe按钮。

b. 在串口输出上,可以观测到这一过程,IP已经从观测状态O,进入了IDLE状态I:

等待command_busy上面显示的箭头消失后,说明该命令已经执行完毕,可以输入下一条命令了。

c. command_code输入 C00_0000_0001,这是IP的插错指令,表示在存储单元address 0x1上,进行内容的反转。除了第一个hex字符表示插错指令,后面10个hex字符用于填写插错的地址。按一下command_strobe按钮;此时对应串口的显示。

d.由于IP只有在Observation状态才能检测错误并且纠正错误,所以我们还需要使用指令A00_0000_0000,使IP回到正常工作状态:

e. 观测IP的状态信号,如下:

可以看到status_heartbeat又恢复了跳动;status_observation再次拉高;status_essential信号由于没有开启高级的错误分类功能,因此被置为高。

相应的串口也有详细的报告报出,包括错误的具体地址:

至此,基本的SEM IP的功能均以得到验证。

5. 合入原有设计

现在只要把这个SEM IPexample完整合入你原来的工程了。这里提供一个简单的demo设计,本身的功能是按一定次序循环点亮开发板上的LED灯。只要给这个设计再添加一个顶层top文件,把原有LED点亮的设计和SEM IP example调用合入即可。如下图:

重新编译,开启了SEU保护的整个设计就完成了。

结 语

本文介绍了如何把一个具有最基本检错纠错功能的SEM IP合入到你的设计当中去。观测SEMIP的状态输出信号,或者查看串口打印的报告,你就已经可以知道设计当前是否正常运行,还是已经出现了SEU错误,并且相应做出正确决策了。

对于绝大多数设计来说,这一基本功能就已经完全够用。你的设计已经开启了SEU保护,可以应对90%以上的SEU事件了。