作者:Lauren Gao,来源: Xilinx赛灵思官微微信公众号

FPGA 设计是有章可循的,如果用的是 Xilinx 的 FPGA,这个“章”就是 UG949。最新版的 UG949 是 2020.1 版本,整个文档共六大章节 306 页(点击此处查看《UltraFast 设计方法指南》)。对于如此之多的内容该如何消化吸收呢?首先,了解一下 UG949 的背景信息。

UG949 是什么?

UG949 是很多工程师的经验总结,这些经验总结告诉我们在实现 FPGA 设计时该如何去做,例如:PCB 设计时的注意事项、什么才是良好的代码风格、时序约束该怎么做、时序收敛有哪些方法等等。

为什么要用 UG949?

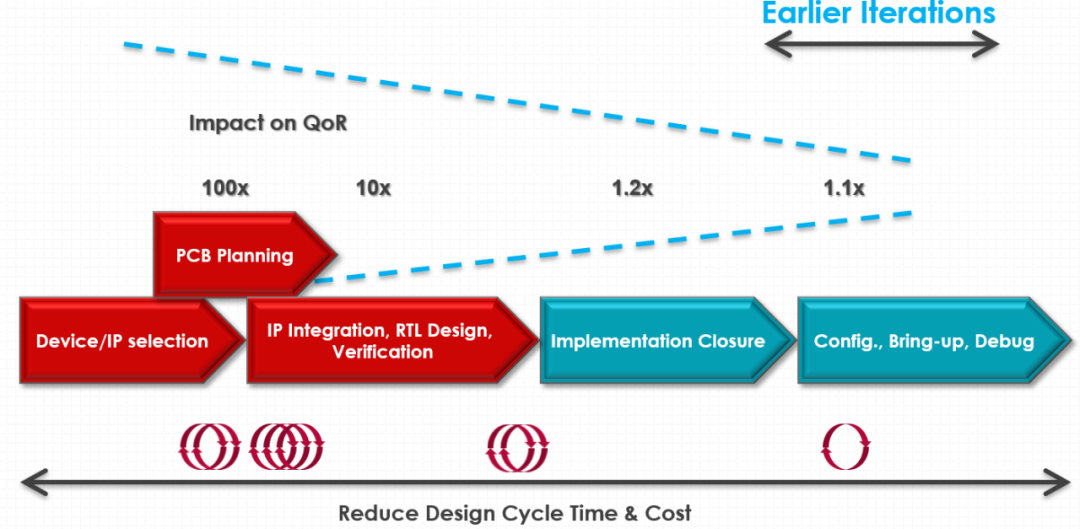

随着微电子工艺的不断发展,FPGA 的规模也越来越大,例如出现了多 die 芯片(SSI 器件),随之 FPGA 设计也越来越复杂,这意味着发现设计潜在的问题并解决也变得愈发困难。

好在 Xilinx 推出了新一代开发工具 Vivado,同时 UG949 也应运而生。从而,工程师们可以遵循 UG949 的设计方法最大可能地避免一些问题并从中找到一些解决问题的方法。简言之,UG949 的核心思想就是尽可能地帮工程师在设计初期发现问题并解决问题,最大化地提升开发效率,降低迭代周期。这是因为问题发现地越晚,解决起来越困难。

UG949 面向哪些对象?

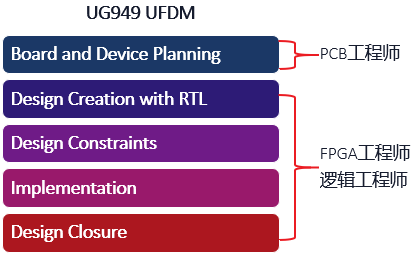

UG949 不仅仅是面向 FPGA 工程师,也面向 PCB 工程师和逻辑工程师,三类工程师均可从中受益。这是因为 UG949 既涵盖了片外板级相关内容,例如 DDR 存储器接口电路设计规则、高速收发器电路设计规则、FPGA 配置电路设计规则、系统级功耗解决方案等,也涵盖了片内设计规则的相关内容,例如设计流程、代码风格、时序约束和时序收敛等,如下图所示。

如何阅读 UG949?

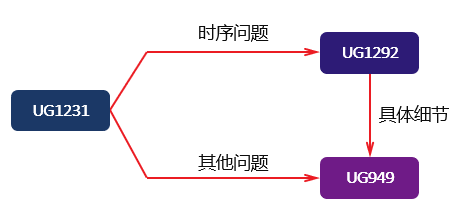

事实上,跟 UG949 相关的文档包括 UG1231、UG1292 和 XTP301。如果把 UG949、UG1231 和 UG1292 打包看作一部字典的话,那么 UG949 就是字典的正文,UG1231 就是字典的索引(只有两页),UG1292 则是字典部分内容的浓缩精华版。既然是字典,我们就不需要从头到尾一页一页地读,而是根据工作需求结合索引,做到有的放矢,达到事半功倍。

例如,如果你是 PCB 工程师,打开 UG1231,浏览到 PCB Designer 部分,会引导你查看 UG949 的 Board and Device Planning 章节,除此之外,如果设计中用到 DDR 存储器,还需要根据 Memory Interface IP Design Checklists 对相关电路进行检查核对,同时根据芯片型号选择相应的 Schematic Design Checklists 对相关电路进行检查核对。

如果你是逻辑工程师,已到了设计的中后期,需要处理时序违例问题,打开 UG1231,浏览到第 2 页,会引导你查看 UG949 Design Closure 章节。这章内容的核心部分之一是 Timing Closure,共 88 页。这 88 页内容已浓缩到 UG1292 中,因此时序问题可首先查看 UG1292。

阅读流程如下图所示。

如何使用 UG949?

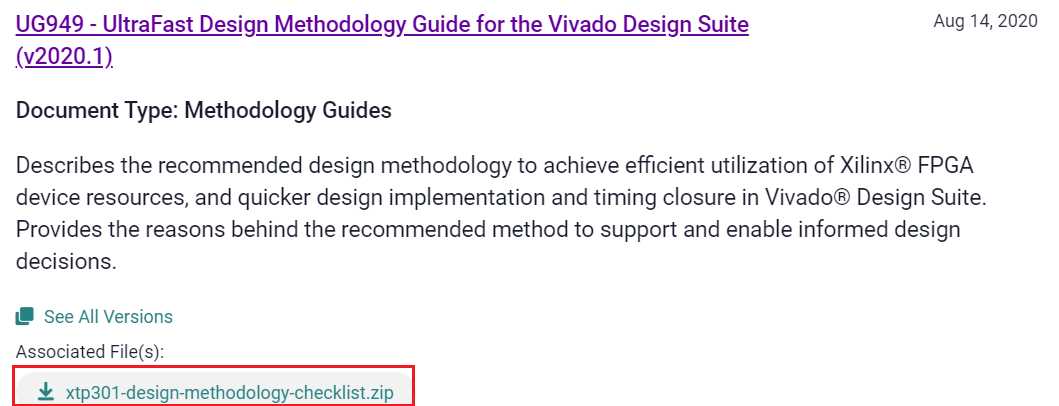

为了帮助工程师们有效地使用和借鉴 UG949 中的设计方法,Xilinx 专门提供了 UFGM 检查表 XTP301。这个表格可以从 Xilinx 官网下载,也可以从 Documentation Navigator 直接生成,如下图所示。

其它相关文档(需登录 Xilinx 账号)

XMP277:7 Series Schematic Review Recommendations