FPGA开发技巧备忘录——modelsim独立仿真vivado平台工程

judy 在 周四, 08/18/2022 - 10:00 提交

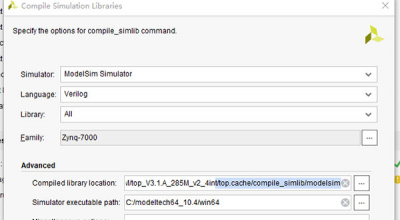

如果只是纯的.v文件仿真那很容易操作,主要是涉及到IP核,那么就必须要对vivado的IP核的库文件进行编译

如果只是纯的.v文件仿真那很容易操作,主要是涉及到IP核,那么就必须要对vivado的IP核的库文件进行编译

在FPGA的设计中的DFX主要是包括可测试性设计和可维护性设计这2大点。最终的目的是快速定位板上问题和后期维护阶段日常巡检诊断。

在调整 FPGA 管脚之前必须熟悉的几点注意事项。

该系列的第二部分描述了一种可能的双时钟设计的架构。在第三部分中,我们将探索另一种选择双时钟 FIFO 架构

面向安全关键领域的 RT-Thread 专业版高安全实时操作系统近日已实现了对于AMD 赛灵思自适应平台的全面支持

图像在采集和传输的过程中,通常会产生噪声,使图像质量降低,影响后续处理。因此须对图像进行一些图像滤波、图像增强等预处理

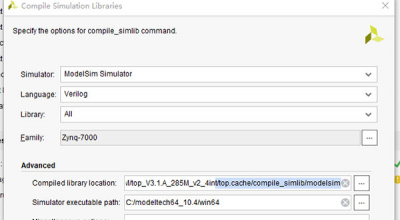

一片RAM中分为许多小格,每一片容量为36k,根据设定的位宽决定了这片RAM可以存放分为几格

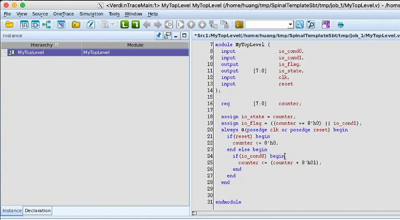

本篇文章来源于微信群中的网友,分享下在SpinalHDL里如何丝滑的运行VCS跑Vivado相关仿真。

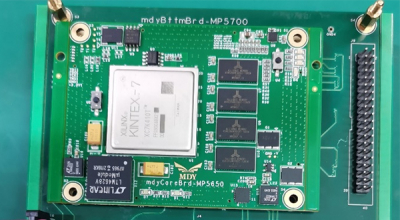

IBERT ip的设置非常简单,只要设置好serdes管脚对应的信息即可,生成的example直接是可以生成bit

本测试实例教程使用IBERT工具对与SFP连接的GTX进行5 Gbps速率下的测试。