FPGA 管脚的调整

随着 FPGA 的不断开发,其功能越来越强大,也给其布线带来了很大的便捷性—管脚的调整。

对于密集的板卡,走线时可以不再绕来绕去,而是根据走线的顺序进行信号的调整,然后通过软件编程来校正信号的通信就可以了。在调整 FPGA 管脚之前必须熟悉几点注意事项。

FPGA 管脚调整的注意事项

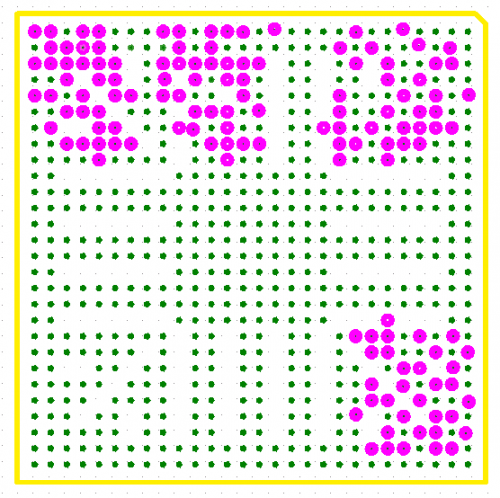

(1)如图 12-1 所示,当存在 VRN/VRP 管脚连接上 / 下拉电阻时,不可以调,VRN/VRP 管脚提供一个参考电压供 DCI 内部电路使用,DCI 内部电路依据此参考电压调整 I/O 输出阻抗与外部参考电阻 R 匹配。

(2)一般情况下,相同电压的 Bank 之间是可以互调的,但部分客户会要求在 Bank 内调整,所以调整之前要跟客户商量好,以免做无用功。

(3)做差分时,“P”“N”分别对应正、负,不可相互之间调整。

(4)全局时钟要放在全局时钟管脚的 P 端口,不可以随便调整。

图 12-1 FPGA 管脚调整的注意事项

FPGA 管脚的调整技巧

(1)为了方便识别哪些 Bank 之间可以互调,必须先对 FPGA 各个 Bank 进行区分。在原理图编辑界面中,执行图标命令“交叉探针”,单击某个 FPGA 的某个 Bank,直接跳转到 PCB 中相对应的 Bank 管脚高亮,这时可以在某一机械层添加标注,进行标记,如图 12-2 所示。

图 12-2 Bank 的标记

(2)按照相同的操作方法可以把调整 Bank 在 PCB 中进行标记,如图 12-3 所示。

图 12-3 被标记的 FPGA

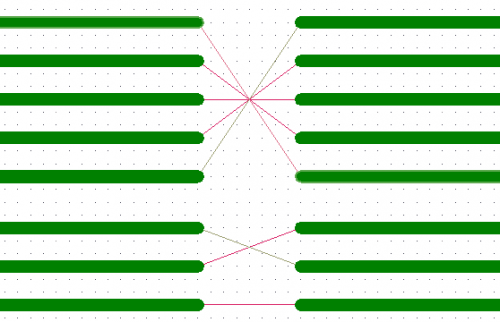

(3)完成上述步骤之后,就可以按照正常的 BGA 出线方式把所有的信号脚进行引出,并按照走线顺序对接排列,但非连接上,如图 12-4 所示,飞线是交叉的,但是不直接连上。最后保存好所有文档。

图 12-4 信号走线的对接

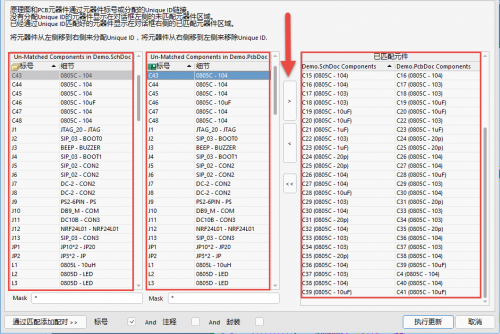

(4)在 PCB 设计交互界面中,执行菜单命令“工程 - 元器件关联”,进行元件匹配,将左边元件全部匹配到右边窗口,单击“执行更新”按钮,执行更新,如图 12-5 所示。

图 12-5 元件的匹配

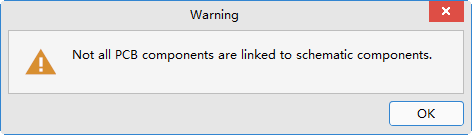

(5)执行菜单命令“工具 - 管脚 / 部件交换 - 配置”,定义和使能可调换管脚元件,如果弹出警告,须重新返回第(4)步进行操作,或者执行从原理图导入 PCB 的操作,使原理图和 PCB 完全对应上之后再按照此步骤进行操作,否则会弹出如图 12-6 所示的警告信息。

图 12-6 警告信息

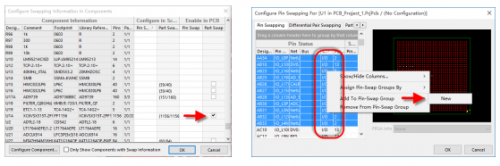

(6)找到 FPGA 对应的元件位号,勾选使能状态,双击该元件,对该元件的可以调换的 I/O 属性管脚创建 Group 操作,单击“OK”按钮,设置完毕,如图 12-7 所示。

图 12-7 可调换 FPGA 的使能及 Group 设置

(7)执行菜单命令“工具 - 管脚 / 部件交换 - 交互式管脚 / 网络交换”,单击之前对接的信号走线,进行线序调换。注意:“Project”工程文件一定要保存一下,再操作。

执行完上述步骤之后,PCB 管脚调换的工作就完成了,具体效果如图 12-8 所示。

图 12-8 线序的调换调整

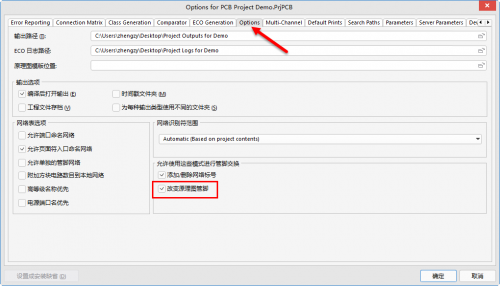

(8)PCB 执行调换更改之后,需要把网络交互反导入原理图,如图 12-9 所示,执行菜单命令“工程 - 工程选项”,勾选反导入选项“改变原理图管脚”。

图 12-9 反导入原理图设置

(9)在 PCB 设计交互界面中,执行“Update Schematic in Project”命令,按照之前原理图导入 PCB 那样的方法,完成 PCB 导入原理图。

因为有些原理图绘制的方式或格式错误,执行反标可能不完全或残缺,建议反标之后利用正导入方式核对一遍或者直接手工方式绘制管脚更换表,再一一进行比对更改。