Versal ACAP 硬件、IP 和平台开发方法指南

judy 在 周三, 02/16/2022 - 10:19 提交

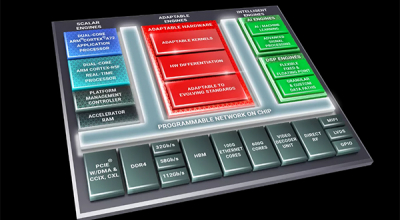

赛灵思 Versal® 套件计算加速平台 (ACAP) 设计方法论是帮助 Versal 设计流程的一整套计算实践。这必须让用户进行这些设计的操作下载能力和复杂性,因此通过特定的步骤设计任务确保设计完成并成功完成。

赛灵思 Versal® 套件计算加速平台 (ACAP) 设计方法论是帮助 Versal 设计流程的一整套计算实践。这必须让用户进行这些设计的操作下载能力和复杂性,因此通过特定的步骤设计任务确保设计完成并成功完成。

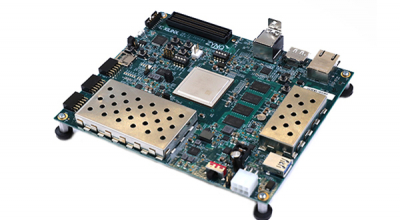

ZCU104 开发板基于Xilinx 公司Zynq UltraScale +XCZU7EV-2FFVC1156 MPSoC器件设计,支持嵌入式视觉使用案例的许多常见外设及接口

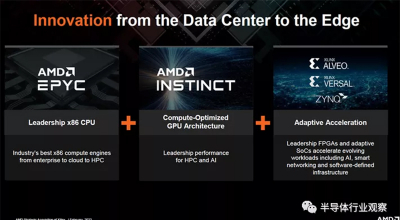

过去几年里,计算行业见证了数据的大规模爆发以及机器学习( ML )与 AI 应用的激增。其结果是对更高吞吐量和实时计算能力愈发强烈的需求,与此同时还要保持灵活应变能力,以便跟上不断演进的工作负载需求和不断变化的协议。

AMD 周一宣布完成了对 Xilinx 的收购,创建了一家可以提供各种类型计算设备的公司,当中包括 CPU、GPU 和 FPGA。此举将帮助 AMD 继续扩大其在数据中心领域的影响力

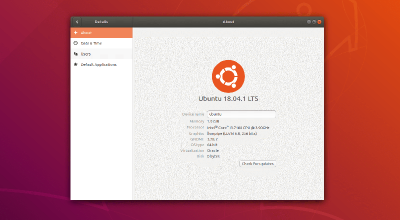

在Ubuntu 18.04下使用Vivado Jtag加载FPGA,发现找不到器件。

AMD今天宣布以全股份交易(all-stock transaction)方式完成对赛灵思(Xilinx)的收购。

在解答相关问题的时候有碰到过cl_invalid_work_group_size的错误,然后通过报错信息在XRT

本文介绍了当MicroBlaze包含在DFX可重构模块(RM)内时,更新MicroBlaze Block RAM的内容。

这种眼动追踪辅助技术可用你的眼睛创建一个交流工具来增强运动控制。通过校准眼球运动,该技术使用人工智能来跟踪角膜反射和瞳孔定位。 通过交互式演示,您可以进行校准,然后玩各种展示眼动追踪技术的游戏。

在Vivado中,可能由于某些逻辑输入悬空而导致Implementation的opt_design时会错