赛灵思 Versal® 自适应计算加速平台( ACAP )设计方法论是旨在帮助精简 Versal 器件设计进程的一整套最佳实践。鉴于这些设计的规模与复杂性,因此必须通过执行特定步骤与设计任务才能确保设计每个阶段都能成功完成。建议您遵循这些步骤和最佳实践进行操作,这将有助于您以尽可能最快且最高效的方式实现期望的设计目标。

系统设计类型

Versal ACAP 属于异构计算平台,具有多个计算引擎。在 Versal 上可映射各种应用,包括对无线系统、机器学习推断和视频处理算法进行信号处理。除了多个计算引擎外,Versal 还可使用高速串行 I/O、NoC、DDR4/LPDDR4 存储器控制器和多重速率以太网媒体访问控制器( MRMAC )来提供超高系统带宽。

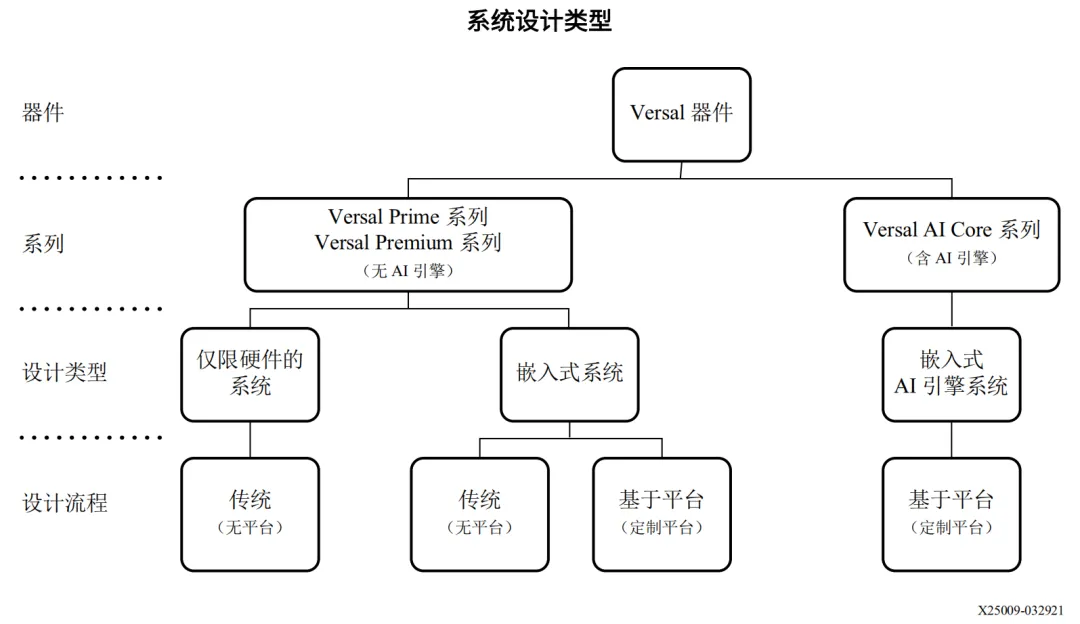

针对 Versal 器件中的Versal Prime、Versal Premium 和 Versal AI Core 系列,下图显示了每种系列所支持的不同系统设计类型和设计流程。

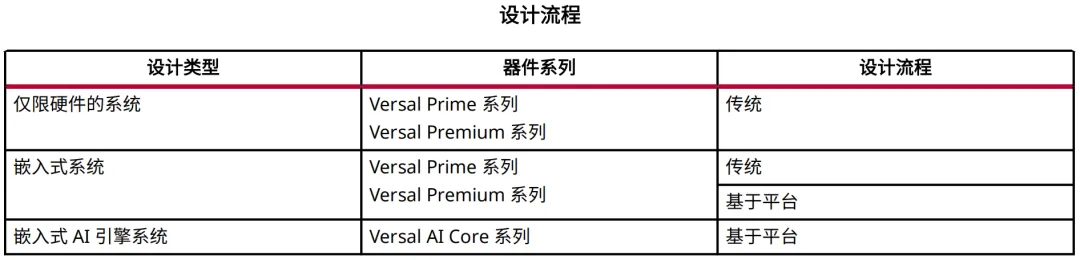

下表显示了每种 Versal 器件系列所支持的系统设计类型和设计流程。如该表中所示,大部分设计流程都以构建平台为基础。

您可以访问赛灵思 GitHub 获取更多示例,这些示例定期更新。

Versal ACAP的设计流程

传统设计流程(无平台)

在传统设计流程中,系统的整个 PL 部分都是在单个 Vivado 工程中定义的。该工程必须包括 Versal 基础硬件 IP 块,以及工程所需的任何其它定制 RTL 和 IP 块。

设计源文件将添加到 Vivado 工具中,并通过 Vivado 实现流程进行编译。如果系统仅包含 PL 组件,那么可使用 Vivado 工具来生成可编程器件镜像( PDI ),以便对 Versal 器件进行编程。如果系统还包含嵌入式软件内容,那么将在从 Vivado 工具导出的固定硬件设计上的 Vitis 环境中开发软件应用。此流程类似于用于 Zynq UltraScale+ MPSoC 的传统流程。

基于平台的设计流程(定制平台)

在基于平台的设计流程中,系统分为 2 个不同元件,即平台和处理器系统。该平台是一种正规化的设计资源,包含用于构建和集成完整工作系统的 Versal 基础硬件 IP 块和软件功能。

该平台的硬件部分是一个专用 Vivado 工程,其中包含最少的必需硬件 IP 块。将软件组件与硬件封装在一起以创建定制平台。处理器系统由实现系统主要功能的 PS、PL 和可选的 AI 引擎功能组成。可以使用 Vivado 工具或 Vitis 环境创建这些不同的元件。然后使用 Vitis 环境将这些元件集成到平台中。该流程促进了系统不同元件的并行开发,并加快了异构系统的集成进程。

Versal ACAP 支持 2 种设计流程:传统设计流程和基于平台的设计流程。要充分利用 Versal ACAP 资源,重要的是选择正确的设计流程。下表显示了根据设计类型和目标器件系列所使用的设计流程。

了解Versal ACAP 设计方法论的概念

从设计之初即采用正确方法,从早期阶段开始对设计目标(包括 IP 选择和配置、块连接、RTL、时钟、I/O 接口和 PCB 管脚分配)给予足够的重视,对于确保设计成功都至关重要。在每个设计阶段中务必正确定义和确认设计,这有助于缓解在子系统和完全集成的系统的实现阶段中出现的时序收敛、性能收敛和功耗使用问题。

创建和实现硬件设计

完成器件 I/O 管脚分配、PCB 布局规划并决定使用模型后,即可开始创建设计。设计创建包括:

• 规划设计的层级

• 识别要在设计中使用和定制的 IP 核

• 例化 IP 目录中不可用的特殊互连或功能所需的 RTL 模块

• 创建时序约束、功耗约束和物理约束

• 指定综合与实现阶段所使用的其它约束、属性及其它元件

创建设计时,主要的考虑要素包括:

• 实现所需的功能

•按期望的频率运行

• 按期望的可靠程度运行

•符合硅片资源和功耗预算要求

在此阶段做出的决策将影响最终产品。在这一阶段的错误决策会导致后续阶段问题层出不穷,进而造成整个设计周期中不断返工。在此过程中尽早花时间详细规划设计有助于达成设计目标并最大限度缩短实验室中的调试时间。

在开发周期早期最大限度扩大影响

如下图所示,设计流程的早期阶段(C、C++ 和 RTL 综合)对于设计性能、密度和功耗的影响远超后期实现阶段的影响。因此,如果设计不满足时序、时延或功耗目标,赛灵思建议您重新评估综合阶段(包括 C、C++、HDL 和约束),而不是仅在实现阶段通过迭代来寻找解决方案。

在每个设计阶段进行确认

Versal ACAP 设计方法强调对设计预算(例如:面积、功耗、时延和时序)进行监控以及尽早采取如下措施更正设计的重要性:

• 尽可能多加利用 Versal ACAP 集成块,使用片上网络( NoC )实现高带宽连接并在模块框图级别确认设计性能。

• 利用赛灵思模板创建最佳 RTL 结构,并在执行细化后进行综合前采用方法 DRC 来确认 RTL。

• 在综合后开展时序分析。

• 通过运行非关联综合和实现来确认每个主要 PL IP 或模块框图的时序收敛可行性。

• 在继续执行下一个设计阶段前采用正确的约束满足时序要求。

使用设计方法论 DRC

Vivado Design Suite 包含一组方法论相关 DRC,可供您使用 report_methodology Tcl 命令来运行。此命令针对以下每个设计阶段都具有相应的规则:

• 在综合前,在细化 RTL 设计中用于确认 RTL 结构。

• 在综合后,用于确认网表和约束。

•在实现后,用于确认约束和时序相关问题。

除了上述关于 Versal ACAP 设计方法论的基本阐述,本指南还包含 8 大主题的高层次信息、设计指南和设计决策利弊取舍,包括设计规划、使用块设计来创建设计、使用 RTL 创建设计、使用 Vitis HLS 创建设计、I/O 管脚分配设计流程、设计约束、设计实现、Vitis 环境嵌入式平台创建方法。

如需查看完整版指南,请点击链接下载:https://app.ma.scrmtech.com/resources/ResourcePc/ResourcePcInfo?pf_uid=1...