ZYNQ学习之路——在SDx中使用xfOpenCV图像加速处理

judy 在 周五, 11/12/2021 - 10:18 提交

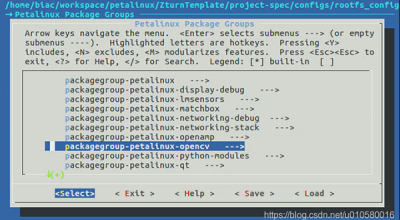

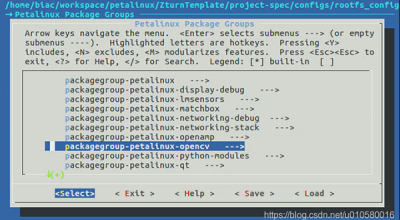

本文以Zturnboard为例介绍如何在SDSoC中使用OpenCV,本文在Ubuntu 16 64位,SDSoC2018.2(安装在ubuntu中)中测试通过。

本文以Zturnboard为例介绍如何在SDSoC中使用OpenCV,本文在Ubuntu 16 64位,SDSoC2018.2(安装在ubuntu中)中测试通过。

Zynq 7020 的 PS 端(ARM 端)的外设 IO(也叫 IOP)分为 MIO 和 EMIO,他们有什么区别呢?

本指南总结了使用 Xilinx® Zynq® UltraScale+™ MPSoC 器件进行设计所需的以软件为中心的信息。

在这个项目中,我将创建一款用于智能办公室移动办公布局的应用。我将使用 Ultra96-V2 演示 Vitis AI 模型库和面向 PYNQ 的 DPU IP 核的编译流程。

虽然看起来AXI Interrupt Controller的intr[0:0]位宽无法修改,但实际上,添加一个Concat IP,这个IP可以设置In0的个数,设置为2。In0连接上中断线后,再把dout和intr相连

在FPGA的开发中,对于两个异步时钟,如果我们可以在RTL的设计中保证这两个时钟域之间的处理都是正确的,那就可以让工具不分析这两个时钟域之间的交互。

随着智能计算逐渐渗透到数字世界的方方面面,如何更高效地应用智能计算,成为所有致力于改变世界的开发者所需面对的关键难题。

美乐威基于赛灵思Zynq® UltraScale+™ EV平台,打造了全新KVM坐席管理系统方案,能够提供前所未有的超低时延、高品质端到端音视频传输,成为千兆网环境部署的理想选择。