基于多级反馈环形振荡器的真随机数发生器设计

judy 在 周一, 11/01/2021 - 10:34 提交

本文提出了一种在现场可编程门阵列(FPGA)上生成真随机数的新方法,该方法以 多级反馈环形振荡器(MSFRO) 的随机抖动为熵源。在传统环形振荡器的基础上,增加了多级反馈结构,扩大了时钟抖动的范围,提高了时钟采样频率和熵源的随机性。与传统的时钟采样结构不同,我们利用MSFRO产生的时钟抖动信号对FPGA的锁相环(PLL)产生的时钟信号进行采样。

本文提出了一种在现场可编程门阵列(FPGA)上生成真随机数的新方法,该方法以 多级反馈环形振荡器(MSFRO) 的随机抖动为熵源。在传统环形振荡器的基础上,增加了多级反馈结构,扩大了时钟抖动的范围,提高了时钟采样频率和熵源的随机性。与传统的时钟采样结构不同,我们利用MSFRO产生的时钟抖动信号对FPGA的锁相环(PLL)产生的时钟信号进行采样。

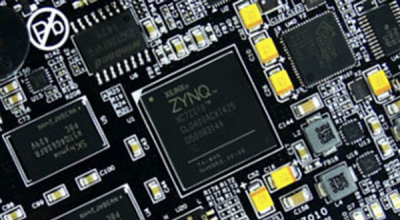

本次设计是在zynq7035器件上进行,创建PYNQ框架v2.6版本,构建需要如下步骤:

国微思尔芯推出在原型验证领域的前沿技术创新产品:芯神瞳逻辑矩阵LX2。逻辑矩阵LX2采用的是赛灵思目前容量最大的UltraScale+ VU19P FPGA芯片。其单系统最多可配置8颗FPGA,而每个标准机柜最高可配置8台LX2,单机柜支持近32亿门逻辑规模

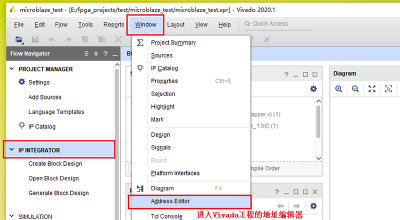

修改了代码后编译工程,有时会因为BRAM空间不足而编译失败,出现下面的错误提示,这时,需要回到Vivado工程里面,在Block Design中将分配的BRAM空间大小改大。具体方法如下。

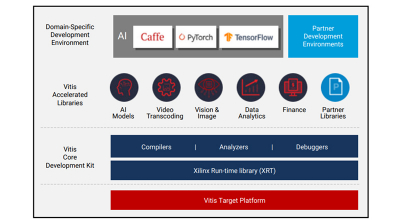

本文描述了两个ML建模应用,用于提高Vivado® ML版中时序延迟和路由拥塞估计的准确性。

本答复记录将介绍在 Vivado 2016.4 - 2017.2 工具中,在 PetaLinux 和独立操作系统下如何使用 MPSoC 器件运行 USB2.0 标准接口。

Kria KV260 超长干货之开箱指南

本文介绍了使用16通道发射(16Tx)和16通道接收(16Rx)子数组的实验结果,其中所有发射和接收信道都使用数字转换器集成电路(IC)中的强化型DSP模块来校准。与其它架构相比,这个多信道系统在尺寸、重量和功率上都更有优势。相对于该系统的FPGA资源利用率后可发现,强化型DSP模块可为多信道平台的设计人员解决重要挑战。

在编写ZYNQ的FPGA逻辑代码过程中,往往需要对时序进行分析。时序信号的分析一般通常有软件仿真和在线仿真两种,本文介绍这两种方法的具体使用方法。