在Vitis IDE 中调用Vitis™视觉库的加速内核实例

judy 在 周四, 06/24/2021 - 10:29 提交

本期视频邀请到赛灵思高级产品应用工程师陈雯,将介绍 Github 上开源的 Vitis 视频加速库的相关内容,并演示在Avleo U50 的板卡上,从Vitis IDE 中调用Vitis™视觉库的加速内核的应用实例解析。

本期视频邀请到赛灵思高级产品应用工程师陈雯,将介绍 Github 上开源的 Vitis 视频加速库的相关内容,并演示在Avleo U50 的板卡上,从Vitis IDE 中调用Vitis™视觉库的加速内核的应用实例解析。

Xilinx推出具有突破性技术的 Vivado ML 以加速设计收敛并提升 QoR,以及先进的 DFX 功能,可实现时间计算的创新形式。

在查看Xilinx KINTEX-7 FPGA存储器资源时,你会发现它的FIFO生成器支持两种读取选项模式——标准读取操作和FWFT读取操作。什么是FWFT?

赛灵思公司今日宣布推出 Vivado® ML 版,这是业内首个基于机器学习( ML )优化算法以及先进的面向团队协作的设计流程打造的 FPGA EDA 工具套件,可以显著节省设计时间与成本。与目前的 Vivado HLx 版本相比,Vivado ML 版将复杂设计的编译时间缩短了 5 倍,同时还提供了突破性的平均达 10% 的结果质量( QoR )提升。

随着移动互联网上内容的爆炸性增长,内容服务提供商开始使用大量动图来吸引用户有限的注意力。为了解决 WebP 动图转码的时延问题,深维科技基于赛灵思 Alveo™ U200 加速卡打造了 ThunderImage GIF2WebP 动图转码解决方案。

为提升女性在技术职业中的表现、参与度以及创业技能和能力,赛灵思与全球重点大学一起发起全新的技术女性 WIT 资助计划,该计划旨在通过设立专项奖金来吸引、发展和鼓励更多女性投身于技术领域职业生涯。

去年,赛灵思推出了 VU57P,为公司业经量产验证的 Virtex® UltraScale+™ HBM FPGA 系列增添了一款“独一无二”的高速器件。VU57P 器件集成 16GB HBM DRAM、58G PAM4 收发器、高性能 FPGA 架构和高速连接硬化 IP。目前,VU57P 器件的量产版本现已供货。

Versal Premium ACAP 系列符合 PCIe 规范修订版 5.0,并且通过每通道 32 GT/s 的传输速度支持全部链路速率。 本视频演示了 Versal Premium ACAP 中面向 PCIe 的两个可用子系统,这在下一代网络和云基础架构中至关重要。

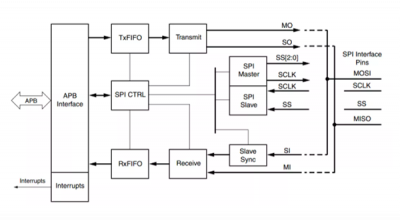

SPI 总线控制器支持与各种外设通信,例如存储器、温度传感器、压力传感器、模拟转换器、实时时钟、显示器和任何支持串行模式的SD卡等等。SPI 控制器可以在主模式、从模式或多主模式下工作。Zynq-7000 器件包括两个 SPI 控制器,该控制器基于 Cadence SPI 内核。

当在硬件配置中包含“大型发送卸载 (Large Send Offload)”并在缓冲区描述符中启用 LSO 功能时,GEM IP 可能通过中断状态寄存器的位 6(同样反映在发射状态寄存器的位 4 中)错误触发“amba error”中断事件。除了误报此错误外,并未观测到任何功能性问题,且仍可继续使用 LSO 卸载功能。