【工程师分享】在FreeRTOS的main()函数里初始化设备,不能收到中断

judy 在 周五, 02/05/2021 - 09:44 提交

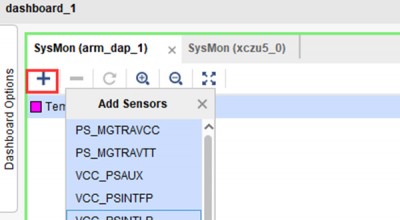

FreeRTOS在 void vTaskStartScheduler( void )里调用 configSETUP_TICK_INTERRUPT(), 也就是void FreeRTOS_SetupTickInterrupt( void )。void FreeRTOS_SetupTickInterrupt( void )在文件portZynqUltrascale.c里实现