泰克:引领数字时代,利用 Xilinx SoC 升级入门级示波器

judy 在 周六, 02/20/2021 - 10:12 提交

由于优异的性能和丰富的功能集,泰克选择了赛灵思 Zynq-7000S SoC。借助 Zynq-7000S 器件,泰克可以更改 TBS1000C 的用户界面,使其与泰克的其他产品匹配。Zynq-7000S SoC 能够将记录长度增加 8 倍,并将波形捕获速率提高 10 倍,在缩短上市时间的同时,实现先进的软件功能和采集功能。

由于优异的性能和丰富的功能集,泰克选择了赛灵思 Zynq-7000S SoC。借助 Zynq-7000S 器件,泰克可以更改 TBS1000C 的用户界面,使其与泰克的其他产品匹配。Zynq-7000S SoC 能够将记录长度增加 8 倍,并将波形捕获速率提高 10 倍,在缩短上市时间的同时,实现先进的软件功能和采集功能。

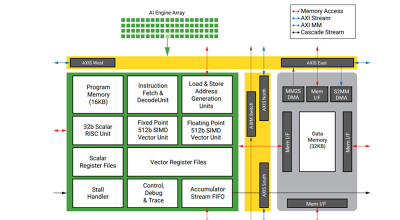

本文重点介绍在Xilinx® Versal™ AI Core器件中使用AI Engine技术的数字下变频链(DDC)设计。展示了一种将DDC功能映射到AI Engine阵列的创新方法,利用Versal ACAP的独特架构来提供高性能和高效率。

详细了解基于 Zynq UltraScale+ MPSoC 视频编解码器单元 (VCU) ROI 的编码参考设计的系统与硬件架构。 在详细了解硬件架构之前,先大概了解一下系统架构。 最后将介绍用于启动参考设计的资源。

机器学习 (ML) 技术正在强化交通部门的检测精度和数据分析能力。虽然该技术相对新颖,但它仍在不断演进发展中,且正在成为新的标准。智能交通摄像头广泛应用于收费系统、交通监控、安全保障等。这些系统的打造具有变革性的意义,因为与建设分流路线和更多道路的成本消耗相比,它们对于优化交通流,疏解交通拥挤和堵塞意义深远

ADQ32双通道12位数字转换器支持每通道2.5 Gb/s的同步采样,而ADQ33则支持每通道1 GS/s的同步采样,并具有开放的Xilinx Kintex Ultrascale KU040现场可编程门阵列(FPGA) 。这两款数字化仪为高容量应用而优化

通过本视频详细了解基于 Zynq UltraScale+ MPSoC 视频编解码器单元 (VCU) ROI 的编码参考设计的软件架构。 首先,我们将讨论 Xilinx 视频和连接 IP 支持堆栈, 接着,视频将描述 VCU ROI 应用程序的软件堆栈,并详细讨论 Gstreamer 流输出管道、以及 ROI GStreamer 插件和 Gstreamer 流输入管道。

本应用说明提供了使用与标准FPGA I/O耦合的外部硬件的FPGA MIPI D-PHY解决方案。

本视频将演示使用Zynq UltraScale+ MPSoC视频编解码单元,实现基于感兴趣区域的编码,并将其用于广播带宽最大化。

Free RTOS实时操作系统运行环境,这里不深入探讨Free RTOS的具体使用。本实验以FreeRTOS Hello World做举例,并实现两个LED灯以不同间隔持续闪烁。本实验基于 “PL端AXI GPIO的使用”工程,硬件环境不需要修改。

本指南提供新版本的 Vivado® Design Suite 概述,包括有关新增功能和功能变更信息、软件安装需求以及许可信息。其中还提供了已知问题列表,并包含指向可提供最新信息的答复记录的链接。