【北京站】助力中小AI新创企业,2019 Xilinx AI 线下先行者计划系列活动报名开始了!!!

judy 在 周三, 12/05/2018 - 09:12 提交

尊敬的客户:

您好!

在人工智能的浪潮中,依元素科技联合赛灵思、安富利以“聚焦人工智能,助力创新创业”为目标,凭借Xilinx行业领先的技术力量,2018年12月起在全国面向中小AI企业开展一系列的人工智能研讨会,希望帮助中小AI企业成就梦想、同时激发创新机遇。

尊敬的客户:

您好!

在人工智能的浪潮中,依元素科技联合赛灵思、安富利以“聚焦人工智能,助力创新创业”为目标,凭借Xilinx行业领先的技术力量,2018年12月起在全国面向中小AI企业开展一系列的人工智能研讨会,希望帮助中小AI企业成就梦想、同时激发创新机遇。

在goggle上搜zcu102 pynq可以找到一些移植方法的信息

0. Prebuilt

PYNQ移植ZCU102编译好的固件

该培训视频涵盖了 SDAccel RTL 内核向导,并详细介绍了封装 RTL 设计、构建 FPGA 设计和生成 Amazon FPGA 映像(AFI)所涉及的步骤。

与几年前相比,人工智能(AI)市场开始以更快的速度稳固其在现实世界的地位,尤其是初创企业和技术供应商急于创建针对利基解决方案和平台。

根据Tractica的新数据,随着兼并和收购(M&A)活动的加剧,该行业正在迅速发展并关注重点领域。根据调查,AI市场的关键分支包括:

上一节我们观察了AXI总线的信号,了解了基于AXI总线读写的时序,这一节我们继续探索基于AXI总线的设计,来看一看ZYNQ系列开发板的独特优势,PS可以控制PL产生定制化的行为,而不需要去动硬件代码。

在开发PL时一般都会用到分频或倍频,对晶振产生的时钟进行分频或倍频处理,产生系统时钟和复位信号,下面就介绍一下在vivado2017.3中进行PL开发时调用IP的方法。

首先打开vivado2017.3新建一个RTL项目。

点击Flow navigator的IP Catalog 选项,如下图所示:

一. 概述

Xilinx FPGA有三种可以用来做片上存储(RAM,ROM等等)的资源,第一个就是Flip Flop;第二种就是SLICEM里面LUT;第三种就是Block RAMs资源。

在用Vivado建立工程的时候选择器件的时候就可以看到这些资源的多少。如下图所示。

本篇主要介绍TTL/CMOS电平的互连、OC/OD的互连,其余单端逻辑电平的互连可参考相关器件规范、电平规范。

1、TTL/CMOS互连

本培训视频介绍了 AWS F1 硬件平台的技术规格。观看此视频,以了解 AWS FPGA 中的各个区域,了解AWS F1 Shell 并查看重要的性能注意事项。

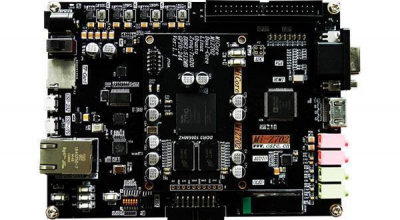

QNX版本:QNX6.6

宿主系统:Windows

交互系统:Debin

开发板:MIZ702 完全兼容ZedBoard