本文转载自:十年老鸟的CSDN博客

TX buffer vs 相位对齐电路

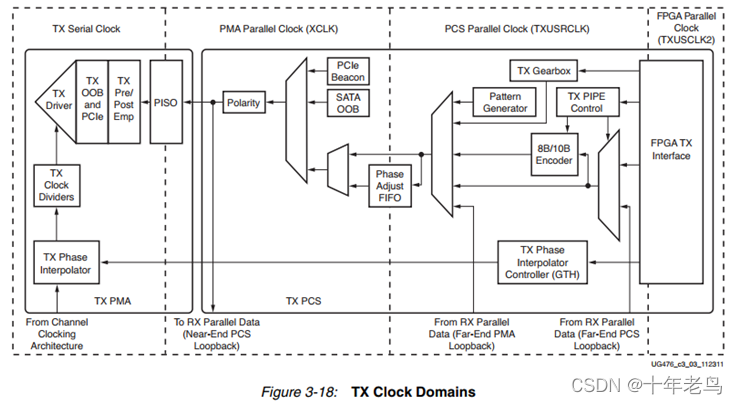

在GTX/GTH收发器 TX链路中有两个内部并行时钟作用于PCS:PMA并行时钟(XCLK)和TXUSRCLK时钟域。为了发送数据,XCLK的速率必须匹配TXUSRCLK的速率,并且两个时钟域所有相位差异必须解决。

GTX/GTH收发器包含一个TX缓冲器和TX相位对齐电路来解决XCLK和TXUSRCLK的相位差异。当TX相位对齐电路使用时TX缓冲器被旁路,所有的TX链路必须要么使用TX缓冲器,要么使用TX相位对齐电路,二者选其一。

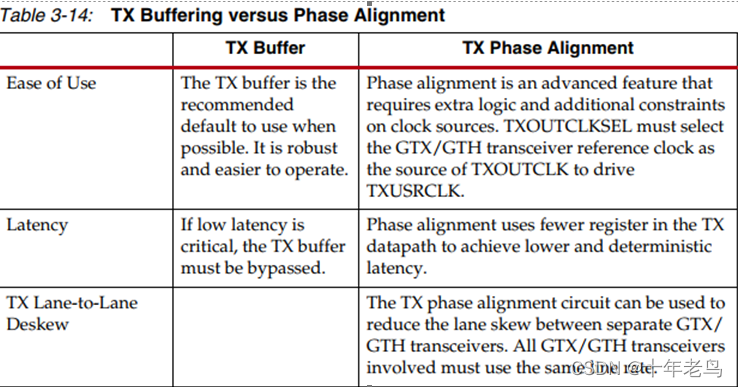

下表列出了这两个功能的优缺点

使用TX buffer 操作起来简单,而且更加健壮。

但对于延时要求比较低以及确定性延迟要求比较高的应用,则不需要将TX buffer旁路。使用TX phase alignment 可以减少各个lane之间的抖动。

在我实际使用中:

因此对于延时要求不高以及确定性延迟要求不高的,最好使用TX buffer。尽管这么看我们的应用延迟越少越好,以及确定性时延越稳定越好。不过似乎由于serdes带来的影响也不至于影响我们的业务,因此这点可以保持关注,不一定需要改什么

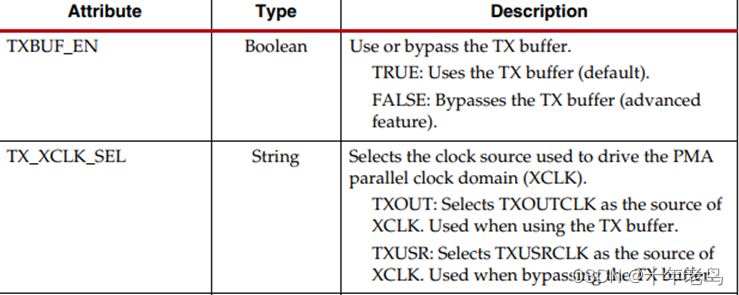

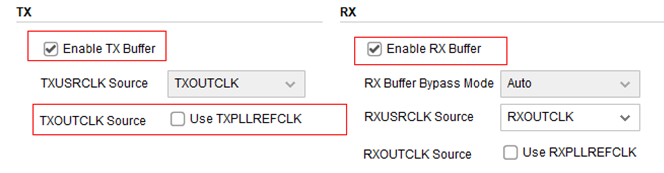

Ip核中使用不使用 TX Buffer在这里设置,

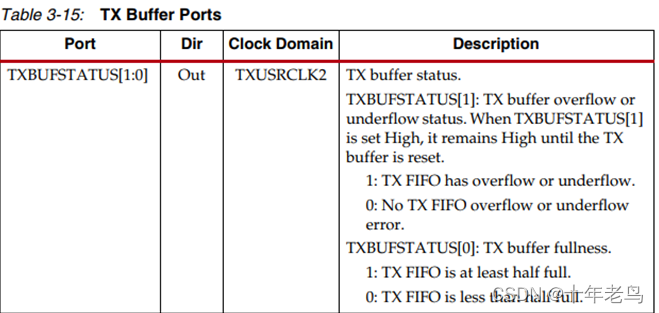

如果使用了TX Buffer,理论上需要监控下面端口的值

这个端口指示TX buffer上溢出还是下穿底,tx buffer可以通过GTTXRESET、GTPCSRESET或者当TXBUF_RESET_ON_RATE_CHANGE = TRUE时在速率改变时候,transceiver内部产生Txbuffer 复位。(如果真的要用直接用GTTXRESET就好)

使能TX buffer下面的条件要设定:

• TXBUF_EN = TRUE

• TX_XCLK_SEL = TXOUT

TX Buffer Bypass

旁路TX BUFFER是7系列GTX/GTH收发器的一个重要特点。TX 相位对齐电路用于调整PISO并行时钟域和TX XCLK时钟域相位差异来从PCS到PISO传输数据。它完成TX的时延对齐通过持续不断的调整TXUSRCLK来进行补偿由于温度和电压的波动。TX相位和时延对齐能够被transceiver自动完成或者用户手动控制。

看到这里发现TX BUFFER旁路掉之后多了以下这两个模块,

gtwizard_0_TX_MANUAL_PHASE_ALIGN

gtwizard_0_RX_MANUAL_PHASE_ALIGN

看来还得回过头来重新复盘一下

gtwizard_0_TX_STARTUP_FSM

gtwizard_0_RX_STARTUP_FSM

这两个模块,发现不勾选TX BUFFER之后,上面两个模块关于相位对齐的功能忽略了。要再研读一下这两个模块里面是怎么进行手动相位对齐操作的

gtwizard_0_TX_MANUAL_PHASE_ALIGN

gtwizard_0_RX_MANUAL_PHASE_ALIGN。

手册中分了:

1、 单条lane情况下手动TX BUFFER旁路模式

2、 多条lane情况下手动TX BUFFER旁路模式

鉴于我目前的应用都是多条lane的情况。那就直接对着代码和手册直接过一下这个多条lane下手动TX BUFFER旁路模式的操作流程

对于GTX和GTH收发器,当多条lane的应用需要TX BUFFER bypass时,相位对齐需要手动执行。

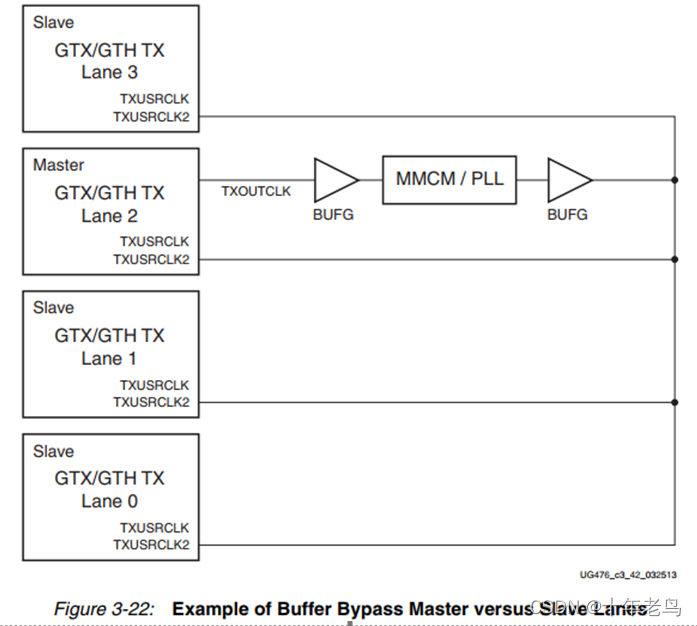

Master:在多条lane应用中,

Master: In a multi-lane application, the buffer bypass master is the lane that is the source of TXOUTCLK.

Slave: All the lanes that share the same TXUSRCLK/TXUSRCLK2, which is generated from the TXOUTCLK of the buffer bypass master.

下面这些必须要设置:

• TXBUF_EN = FALSE.

• TX_XCLK_SEL = TXUSR.

• TXOUTCLKSEL = 3’b011 or 3’b100 to select the GTX/GTH transceiver reference clock as the source of TXOUTCLK

到gtwizard_0_TX_MANUAL_PHASE_ALIGN模块中找到主状态机

开启状态机首先RESET_PHALIGNMENT信号必须为低

1、 INIT

等待RUN_PHALIGNMENT为高(这些信号来源于gtwizard_0_TX_STARTUP_FSM里面),为高高了将每条lane的TXDLYSRESET拉高,并且状态机跳转到WAIT_PHRST_DONE

2、 WAIT_PHRST_DONE

等待各个lane的TXDLYSRESETDONE信号变高后将各个lane的TXDLYSRESET拉低,当所有的lane的TXDLYSRESETDONE都变高时,状态机跳转到M_PHINIT

3、 M_PHINIT

主lane的TXPHINIT拉高,如果主lane的TXPHINITDONE的上升沿检测到,则主lane的TXPHINIT拉低,状态机进入M_PHALIGN

4、 M_PHALIGN

主lane的TXPHALIGN拉高,如果主lane的TXPHALIGNDONE的上升沿检测到,则主lane的TXPHALIGN拉低,状态机进入M_DLYEN

5、 M_DLYEN

主lane的TXDLYEN拉高,如果主lane的TXPHALIGNDONE的上升沿检测到,则主lane的TXDLYEN拉低,状态机进入S_PHINIT

6、 S_PHINIT

所有slave lane的TXPHINIT拉高,如果各个lane的TXPHINITDONE的上升沿检测到,则各个lane的TXPHINIT拉低,当所有的lane的TXPHINITDONE都变高时状态机进入S_PHALIGN

7、 S_PHALIGN

所有slave lane的TXPHALIGN拉高,如果各个lane的TXPHALIGNDONE的上升沿检测到,则各个lane的TXPHALIGN拉低,当所有的lane的TXPHALIGNDONE都变高时状态机进入M_DLYEN

8、 M_DLYEN2

主lane的TXDLYEN拉高,如果主lane的TXPHALIGNDONE的上升沿检测到,表示多条lane的相位和时延对齐完成,状态机进入PHALIGN_DONE

9、 PHALIGN_DONE

继续保持主lane的TXDLYEN为高来调整TXUSRCLK来补偿温度和电压波动,给出相位对齐完成指示 PHASE_ALIGNMENT_DONE = 1

手册上的解释如下,和上面基本相同

1. The sequence of events shown in Figure 3-23 is not drawn to scale.

2. M_* denotes ports related to the master lane.

3. S_* denotes ports related to the slave lane(s).

4. GTX transceiver: Set the PCS_RSVD_ATTR[1] attribute to 1’b1.

GTH transceiver: Set the TXSYNC_OVRD attribute to 1’b1.

PCS_RSVD_ATTR_IN (48’h000000000006),

5. Set TXPHDLYRESET and TXDLYBYPASS to Low for all lanes.

6. Set TXPHALIGNEN to High for all lanes.

7. Assert TXDLYSRESET for all lanes. Hold this signal High until TXDLYSRESETDONE of the respective lane is asserted.

8. Deassert TXDLYSRESET for the lane in which the TXDLYSRESETDONE is asserted.

9. When TXDLYSRESET of all lanes are deasserted, assert TXPHINIT for the master lane. Hold this signal High until the rising edge of TXPHINITDONE of the master lane isobserved.

10. If TXPHINITDONE is High due to the sequence having completed once already,assertion of TXPHINIT causes TXPHINITDONE to deassert. TXPHINITDONE stays

Low for a minimum of one TXUSRCLK cycle.

11. Deassert TXPHINIT for the master lane.

12. Assert TXPHALIGN for the master lane. Hold this signal High until the rising edge of TXPHALIGNDONE of the master lane is observed.

13. Deassert TXPHALIGN for the master lane.

14. Assert TXDLYEN for the master lane. This causes TXPHALIGNDONE to be deasserted.

15. Hold TXDLYEN for the master lane High until the rising edge of TXPHALIGNDONE of the master lane is observed.

16. Deassert TXDLYEN for the master lane.

17. Assert TXPHINIT for all slave lane(s). Hold this signal High until the rising edge of TXPHINITDONE of the respective slave lane is observed.

18. Deassert TXPHINIT for the slave lane in which the TXPHINITDONE is asserted.

19. When TXPHINIT for all slave lane(s) are deasserted, assert TXPHALIGN for all slave lane(s). Hold this signal High until the rising edge of TXPHALIGNDONE of the

respective slave lane is observed.

20. Deassert TXPHALIGN for the slave lane in which the TXPHALIGNDONE is asserted.

21. When TXPHALIGN for all slave lane(s) are deasserted, assert TXDLYEN for the master lane. This causes TXPHALIGNDONE of the master lane to be deasserted.

22. Wait until TXPHALIGNDONE of the master lane reasserts. Phase and delay alignment

for the multi-lane interface is complete. Continue to hold TXDLYEN for the master

lane High to adjust TXUSRCLK to compensate for temperature and voltage variations.

时序图为:

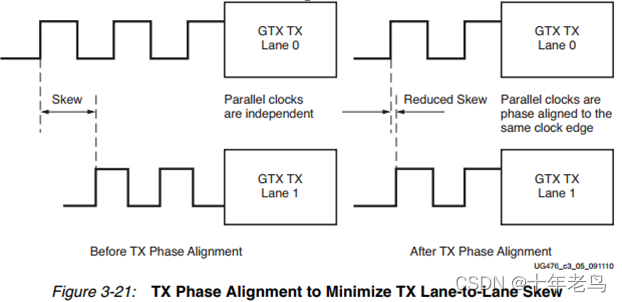

下图是演示Using the TX Phase Alignment to Minimize the TX Lane-to-Lane Skew

TX 相位对齐电路也能减小GTX/GTH收发器之间的抖动。下图展示了TX 相位对齐电路是如何减小lane之间的抖动,通过将多个GTX/GTH transceiver 的XCLK时钟域对齐到一个共同的时钟源。下图展示了多个GTX/GTH transceiver lane在运行相位对齐到同一个时钟源之前和之后的情况。在TX相位对齐之前,所有的XCLK都有不同的相位偏差,在相位调整之后,仅仅的相位差异就是同一个时钟的偏斜。

总结

因为我使用的场景有限,目前暂时感受不到TX buffer 使能与旁路对性能会造成什么影响。但从手册已经程序的学习来看。不使用TX buffer 可以让时延更准确,确定性时延更好。

但目前我还有疑问。

1、 例如我们知道JESD是确定性时延要求很严格的,理论上来说不使用TX RX BUFFER更好才对。

但是在JESD204B PHY的IP核里面是这么设置的

所以,这里就有点困惑了,是不是手册上说的那点时延可以忽略不计呢。

是不是勾选Enable TX Buffer 或者 不勾选Enable TX Buffer时延差别也不是很大呢。

而且这里的TXOUTCLK source 没有勾选 Use TXPLLREFCLK。

对应的代码

.TXOUTCLKSEL (3'b010),

也就是使用的TXOUTCLKPMA path的时钟源,

这里为什么不适用TXPLLREFCLK_DIV1 path呢,也就是手册推荐的一般应用都用TXOUTCLKSEL = 3‘b011 ?

TXOUTCLKSEL = 3’b010 和 TXOUTCLKSEL = 3‘b011 是不是区别不大呢?

这个地方有待理解

因此,我觉得,后面的应用还是勾选enable TX BUFFER。到时候真的碰到什么问题再说,感觉不会有什么影响