Zynq-7000系列Quad-SPI I/O接口简介

judy 在 周一, 09/13/2021 - 09:32 提交

I/O 信号可通过 MIO 引脚获得, Quad-SPI 控制器在共享或单独的总线配置中最多支持两个 SPI 闪存, 控制器支持以多种配置运行

I/O 信号可通过 MIO 引脚获得, Quad-SPI 控制器在共享或单独的总线配置中最多支持两个 SPI 闪存, 控制器支持以多种配置运行

经过前面的实验,我们已经基本摸清楚了Vitis IDE & Vivado的使用方法。在开始构建DPU与深度学习软件栈之前,我们先对我们拿到的开发板做个体检(硬件全面测试),由于大部分深度学习软件框架都是运行在Linux, android或IOS等嵌入式系统上,因此测试完硬件后还需要搭建一个Linux系统以供后续开发使用。

Ubuntu中安装python虚拟环境

本篇笔记以点亮图中所有的LED为目的,回顾下Vivado的使用,并且开始了解Vitis的开发流程(原来开发环境为SDK)。

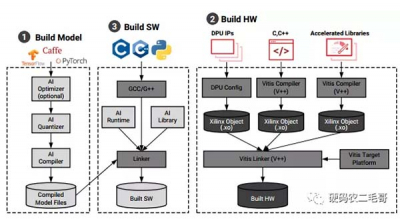

在Vitis AI library中的模型在自定义单板使用中,介绍了如何进行模型库编译,下一步要将模型加入到AI应用中进行编译,生成可执行文件。

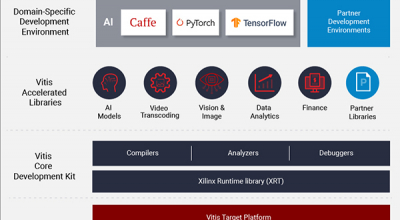

本系列笔记旨在更深入的探索Vitis以及Vitis内部所使用到的技术,本系列主要针对深度学习部署进行探索,比如自定义自己的深度学习硬件平台,深度学习模型量化、模型编译、TVM自动调优,多DPU核异构系统的调度计算等等。

在Vitis AI设计中,构建模型是其中非常重要的一步。如果使用调用的模型库呢?

Vitis AI开发套件提供high-leve C++/Python APIs(VART)进行从云到边器件开发。对于边缘DPU,除了VART,还可以使用advanced low-level C++/Python APIs。

本文对vitis设计流程进行总结

在Vitis下运行DNNDK例程时,(例程地址https://github.com/Xilinx/Vitis-In-Depth-Tutorial/blob/2020.1/Vitis_Plat...)运行到编译时,(20 Right click the hello_dpu project folder and select Build Project)一直出如下错误