Vivado生成bit流失败,怎么解决?

judy 在 周二, 01/19/2021 - 16:02 提交

使用Vivado Runs基础结构时(例如,launch_runs Tcl命令),请将此命令添加到.tcl文件,并将该文件作为执行运行的write_bitstream步骤的预钩添加

使用Vivado Runs基础结构时(例如,launch_runs Tcl命令),请将此命令添加到.tcl文件,并将该文件作为执行运行的write_bitstream步骤的预钩添加

初学 Zynq 的时候,都是按照惯例打开 Vivado 软件,然后实现 Zynq 可编程逻辑硬件部分PL的设置后,把硬件部署导出,再打开 SDK 进行 ARM 核的软件部分 PS 编程设计,最后再将硬件比特流文件(.bit)和软件的可执行链接文件(.elf)下载到 Zynq 开发板中,这样就可以对自己的软硬件设计进行调试和验证。

在开发以太网接口的过程中经常看到 MII、RMII、GMII、RGMII等英文缩写名称。在开发接口前,先将这些名词搞清楚。

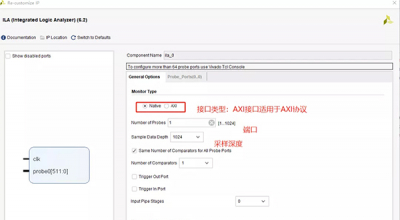

集成逻辑分析仪 (Integrated Logic Analyzer :ILA) 功能允许用户在 FPGA 设备上执行系统内调试后实现的设计。当设计中需要监视信号时,应使用此功能。用户还可以使用此功能在硬件事件和以系统速度捕获数据时触发。

PYNQ框架的设计初衷是通过高层次的封装,将底层硬件FPGA实现细节与上层应用层的使用脱耦,对软件开发者来说,PYNQ框架已经提供了完整的访问FPGA资源的library,让上层应用开发者通过Python编程就可以调用FPGA模块,不需要懂Verilog/VHDL硬件编程就可以享受FPGA可并行计算、接口可方便扩展和可灵活配置带来的诸多好处

图像在采集和传输的过程中,通常会产生噪声,使图像质量降低,影响后续处理。因此须对图像进行一些图像滤波、图像增强等预处理。为改善图像质量,去除噪声通常会对图像进行滤波处理 ,这样既能去除噪声,又能保持图像细节。

并不局限于Vivado一种EDA。头文件主要使用“文件包括”处理,所谓"文件包含"处理是一个源文件可以将另外一个源文件的全部内容包含进来,即将另外的文件包含到本文件之中。Verilog语言提供了`include命令用来实现"文件包含"的操作。

DMA中断实例化函数,将要配置的DMA信息先lookupConfig再进行CfgInitialize,DMA采用块模式(Block mode),如果是Sg模式,则配置失败。定时器初始化函数,传入参数有定时器结构、加载值,设备ID。

本文介绍如何一步一步将设计从SDSoC/Vivado HLS迁移到Vitis平台。

完成Implementation后,在Vivado IDE左侧的Flow Navigator点击Open Implemented Design,然后点击report_utilization。