时序分析

时序分析模块是EDA软件的重要组成部分,核心作用是校验数字电路时序是否符合设计预期,也是验证数字电路时序收敛的重要手段之一。时序分析通过寻找数字电路设计的关键路径、生成时序报告,指导数字电路设计人员修改设计,优化电路时序问题。其中,静态时序分析(STA, Static Timing Analysis)分析的准确度较高,分析过程几乎可以100%覆盖整个数字电路,即每条时序路径都会分析到。

在数字电路设计中使用FPGA作为硬件仿真加速器和原型验证成为主流选择。大规模电路的逻辑分割可以建模为超图划分问题(《面向超大规模芯片验证的分割技术:挑战、算法与实践》),其本质是约束多目标组合优化问题,目前大家普遍采用一种启发式算法,主要的目标还限于割线数量最小化(由于FPGA之间互联资源有限), 没有考虑分割后的实际性能,但在实际使用中DUT的性能是至关重要的一个指标。

因此,在数字前端仿真验证EDA工具中引入STA工具具有多重价值:

❑ 指导分割算法:避免切割关键路径以及避免引入新的关键路径,得到一个性能更优的分割结果

❑ 指导快速分割迭代:在完成分割和TDM Binding后,STA工具可初步估算DUT上板后能达到的性能值,指导快速分割迭代

❑ P&R后性能精准评估:在完成FPGA的布局布线(P&R)并输出了SDF (Standard Delay Format)文件后,STA工具基于SDF文件中的net/cell delay可计算出更加精准的DUT性能值

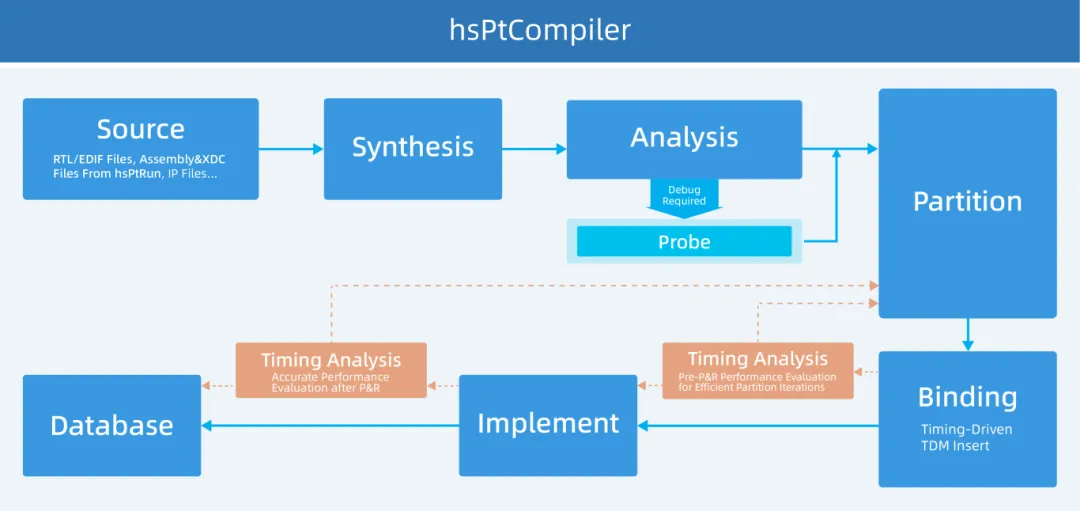

亚科鸿禹硬件验证系统全流程软件编译侧work flow

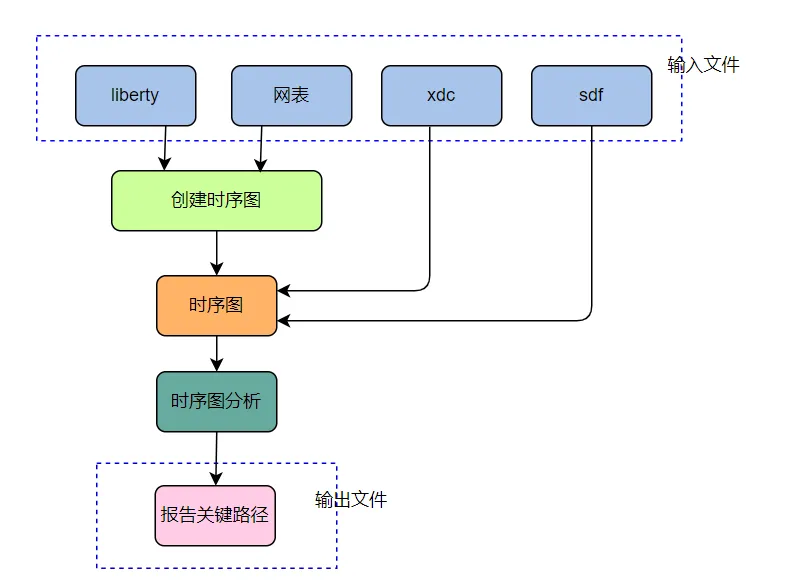

STA核心工作流程:解析输入文件,即用户设计网表和时序相关信息 ➯ 创建时序图 ➯ 分析时序图搜索出关键路径 ➯ 得出在满足时序约束的情况下,用户设计所能达到的最大时钟频率。

时序模型

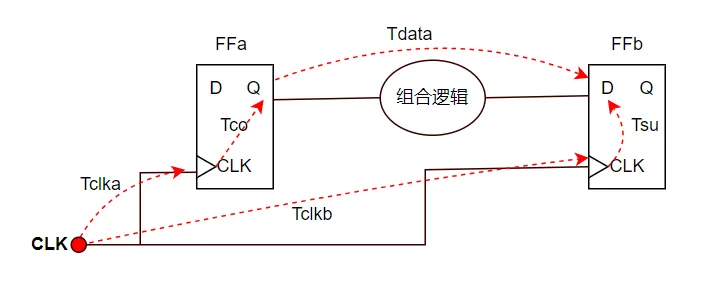

上图是典型的同步时序模型及其时序图,由发起寄存器(FFa)、组合逻辑、捕获寄存器(FFb)及其中间的走线组成。

Tclka是launch clock

Tclkb是capture clock

Tdata是data path delay

Tsetup_slack 是建立时间裕量

Tsetup_slack = Trequired – Tarrival

= (Tcapture + Tcycle – Tsu) – (Tlaunch + Tco + Tdata) ≥ 0

触发器为了能够正确的接收到数据,不出现亚稳态现象,器件本身的特性要求数据到达的时间需要在时钟有效沿到达时间之前,即数据必须在时钟有效沿之前处于稳定状态。对于建立时间,这个时间差越大越好,时间差越大即裕量越大,时序越宽松,从上面的表达式可知,裕量越大,我们可以相应的减小时钟周期(Tcycle),相当于提升工作频率。

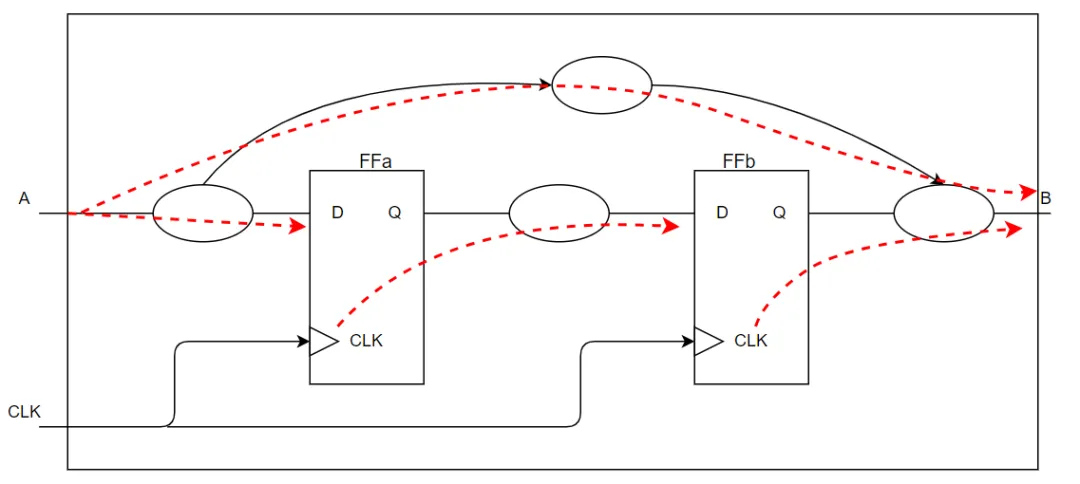

时序路径种类

将电路设计分成时序路径(Timing Path), 然后对电路设计中的每条timing path做时序违例检查,比如检查每条路径的Tsetup_slack是否为负值,如果为负值,表明这条时序路径发生了时序违例,需要设计人员检查原因,修复时序违例。

时序路径分类如下:input port A to FFa/D;input port A to output port B;FFa/CLK to FFb/D;FFb/CLK to output port B

时序分析过程中会穷举包括上面4种类型所有的路径。

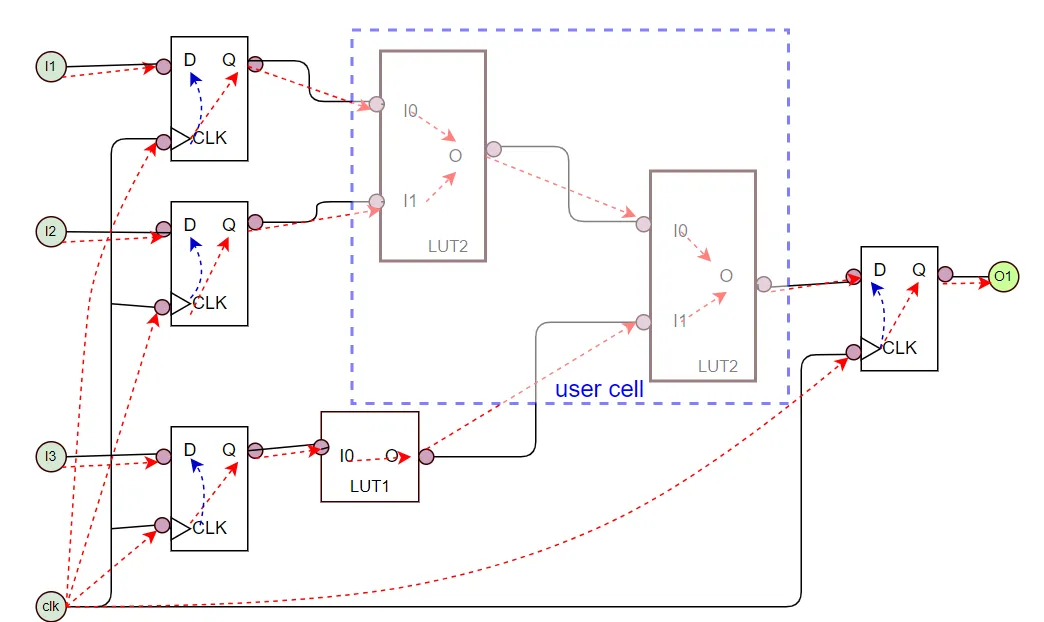

建立时序图

通常读入用户网表,建立相关数据结构,表征了原网表完整的信息,但时序分析只关心网表中与时序相关的信息,比如原子器件间的互联关系,时序无关的信息都被忽略,比如原网表的层级信息,并且原网表构成的是个超图,即一条边可能连接多个节点,总之为了快速有效的进行时序分析,我们需要根据原网表信息建立时序图。

通过对网表的解析,展示各个cell间的互联关系

建立时序图的过程如下:

➯为顶层的每个port创建一个vertex (上图中绿色大圆圈)

➯为每个primitive cell/black box的port创建一个vertex (上图中红色小圆圈)

➯ 根据liberty可知每个cell内部的timing arc, 并且建立一条edge(如lut2中I1到O),其中cell内部的蓝色虚线箭头表示需要做timing check, 一般是setup check

➯ 为每两个port间的互联创建一条edge

最后的时序图由上图中的所有vertex、edge组成,即一个有向图。

DUT设计一定伴随着约束文件,描述系统设计的一些约束信息,其中很大一部分是关于时序约束的,如create_clock/create_generated_clock/set_false_path/set_mutlicycle_path 等,STA工具会将这些信息标注在时序图中,能够分析出更加准确的时序报告。

时序图分析会根据原子器件的特性(从liberty文件中获取,比如哪些地方需要做setup时序检查),在时序图中确定时序路径的起点和终点,然后分析每条路径,进而搜索出关键路径,即最差时序路径(slack最小),分析过程如下:

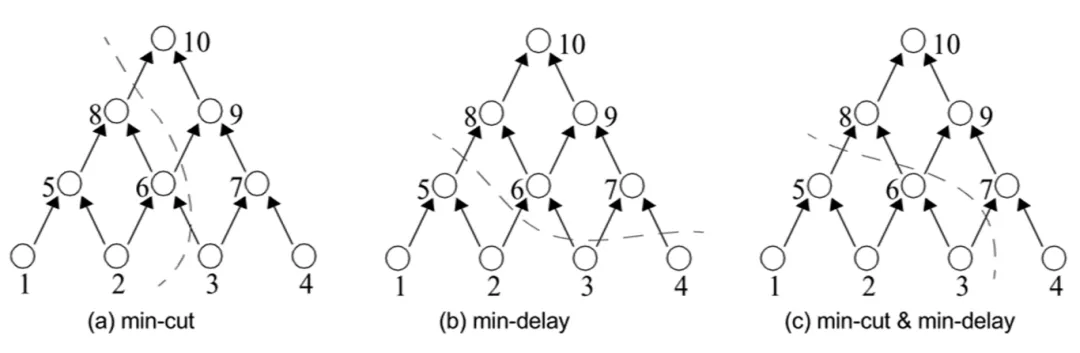

❑ 层级化

从时序路径的起点开始依次给每个节点(vertex)编号,默认起始节点为0,依次增加一个值,例如10,公共节点取较大的值。后面阶段的计算都是按层级方式处理,可以减少计算量,同时也可以采用并行化的方式处理,提高处理速度。

❑ 按层级正向遍历时序图,计算arrival time

假定时序路径的起点arrival time等于0,按层级依次处理每个层级的节点,依据下面公式:

Curarrival time = max(Prearrival time + edge delay, Curarrival time)

❑ 按层级反向遍历时序图,计算required time

按层级反向计算每个节点的required time,依据下面公式:

Currequired time=min(Nextrequired time–edge delay, Currequired time)

❑ 计算每个节点的slack

计算每个节点的slack, 依据下面公式:

Curslack = Currequired time – Curarrival time

基于STA对电路性能的准确分析和多重价值,亚科鸿禹团队为其硬件辅助验证EDA系统自研开发System STA能力,应用于自动编译和深度调试全流程软件flow,显著提升编译调试效率。

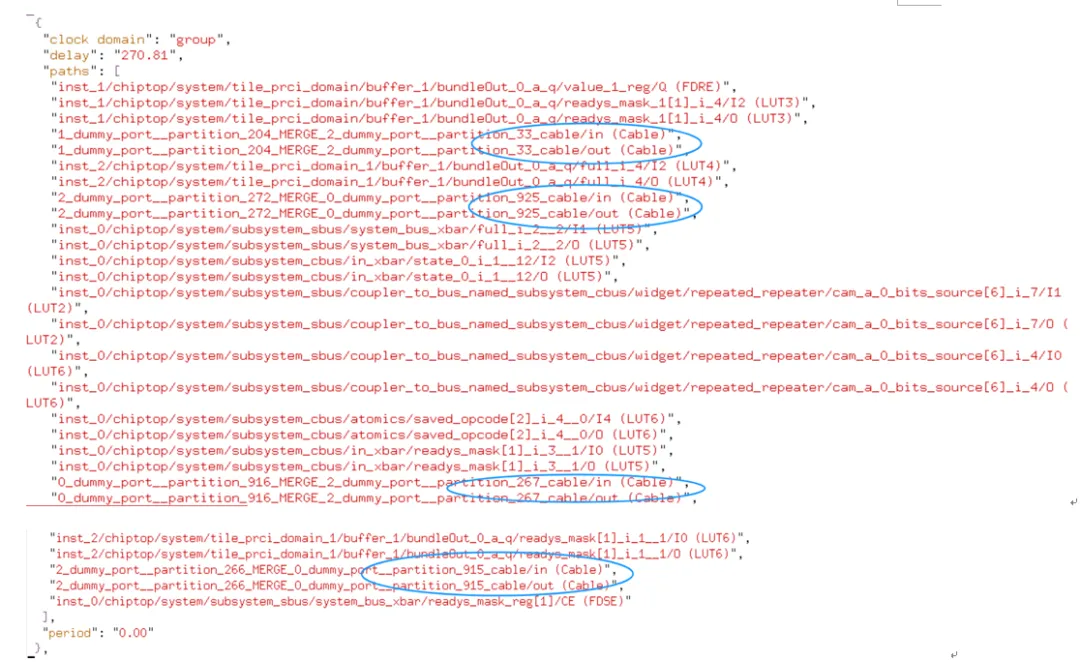

分割结果性能的考核

System STA实现时序图只包含分割边界关联的时序路径,分析时序图找出关键路径,根据关键路径的slack,我们相应调整主时钟频率,在消除所有的时序违例前提下,尽量得到一个最大时钟频率。

比如当前关键路径的slack为负值, 可以相应的降低时钟频率,直到使得关键路径的slack为0, 同理如果当前关键路径的slack为正值,可以相应的提高时钟频率,直到关键路径的slack为0。 总之,最后得到一个当前分割结果使得系统能够正常工作的最大工作频率,作为前面流程的考核,如果性能太差,就需要迭代前面的流程,节省后面流程尝试的时间,同时也为后面上板测试提供指导。

亚科鸿禹硬件验证系统System STA工程应用

指导分割算法

通常由于互联资源的限制,分割算法的目标是减少割线数量,但这样分割的结果并不能保证最后系统性能好坏。为了提高分割结果的性能,我司分割算法也引入了时序分析,由于分割针对的是原始网表,所以需要完整的时序图信息,并采用基于节点的,而非基于路径的分析方法,计算并伴随着多次更新每条边所在最差路径的裕量值,同时为了提高分析,更新时序信息的速度,在多层级分割中分别会为每个层级建立一个单独的,缩小版的时序图,这样分割目标除了最小割线以外,还考虑避免切割关键路径和避免引入额外的关键路径,使得切割后的系统性能最优化。

亚科鸿禹硬件验证系统STA指导分割算法

文章来源:亚科鸿禹