SED简介

FPGA器件在使用中可能会受到质子、中子、α粒子等高能粒子的影响。SRAM 存储单元作为FPGA逻辑配置数据的核心载体,一旦遭遇高能粒子的干扰,有一定的概率发生软错误——这不会永久性损坏器件,但会改变存储单元编程逻辑,随着使用的时间越长,已经发生的错误会不断累积,可能导致设备运行异常甚至任务失败。为解决这一痛点,智多晶在 SA5T-100、SA5T-200 和 SA5T-366 器件中集成了硬核级解决方案——SED(Soft Error Detect)IP核,通过ECC+CRC双校验技术,实现软错误的精准检测、自动纠正与场景化测试,为 FPGA 在极端环境下的稳定运行保驾护航。

SED IP特性

支持校验模式选择

支持1bit或多比特错误检测

支持测试1bit或2bit错误注入

支持自动纠正错误功能

SED IP设计

内部设计核心融合ECC与CRC双校验技术:ECC校验易于硬件实现,可逐帧检错并精准定位1bit软错误位置,实现自动纠正;CRC校验具备更强的错误检测鲁棒性,能有效识别多bit软错误,两者结合为FPGA内部SRAM数据提供可靠监测。

SED IP使用

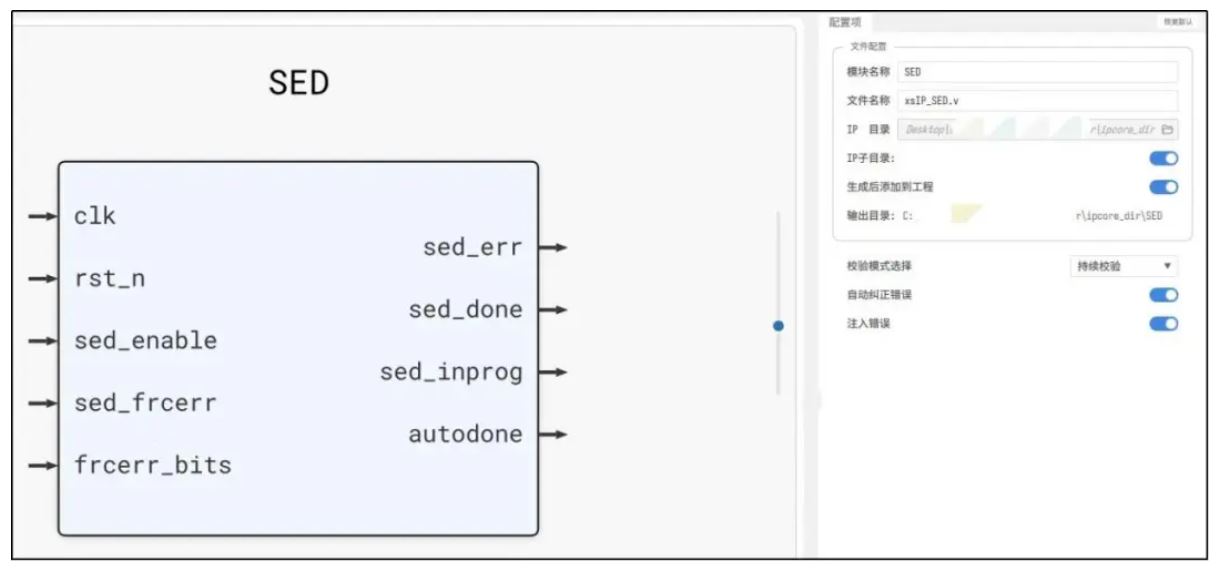

在HqFpga软件打开IP管理界面并搜索SED,即可配置IP相关参数,如图 1所示。用户可在IP配置界面选择一次校验模式或持续校验模式,在持续校验模式下,选择是否打开自动纠正错误功能和注入错误功能,使用起来十分便捷。在使用过程中,只需抓取sed_err输出信号状态,即可检测是否发生错误。

图 1 SED IP配置界面

主要应用场景

医疗设备领域,器件运行在放射性环境

通信设施领域,复杂电磁环境或辐射干扰环境

获取技术文档与DEMO

技术文档获取:SED IP已发布,用户可以在HqFpga软件“IP管理”中打开SED IP界面查看用户指南,或访问智多晶官网(www.isilicontech.com)下载SED IP用户指南。

设计参考案例获取:访问智多晶官网(www.isilicontech.com )下载SED DEMO用户指南。

文章来源:智多晶