文章来源:FPGA入门到精通

这些时钟缓冲器是连接时钟源与时钟网络的"关卡"和"中转站",选择合适的缓冲器至关重要。

7系列FPGA中的时钟缓冲器分为全局时钟缓冲器(Global Clock Buffer)和区域时钟缓冲器(Regional Clock Buffer)。

7系列FPGA中有所谓的局部时钟缓冲器,例如BUFR、BUFMR、BUFIO等,而UltraScale系列FPGA中不再包含这类时钟缓冲器,其功能由新增的BUFGCE_DIV代替。

注意:一般情况下,这些专用时钟缓冲器都是由vivado等软件自动添加。

一、全局时钟缓冲器

全局时钟缓冲器是指基于 BUFGCTRL 配置成的 BUFG 、 BUFGCE 、 BUFGMUX 和 BUFGMUX_CTRL。

1、为什么叫全局时钟缓冲器?

这是因为它们输出的时钟可通过全局时钟树(Global Clock Tree)到达FPGA内部逻辑以及输入/输出逻辑的时钟端口。

输入时钟可来自与之同侧的MRCC 、SRCC 、CMT、BUFG或高速收发器的输出时钟RXOUTCLK/TXOUTCLK。

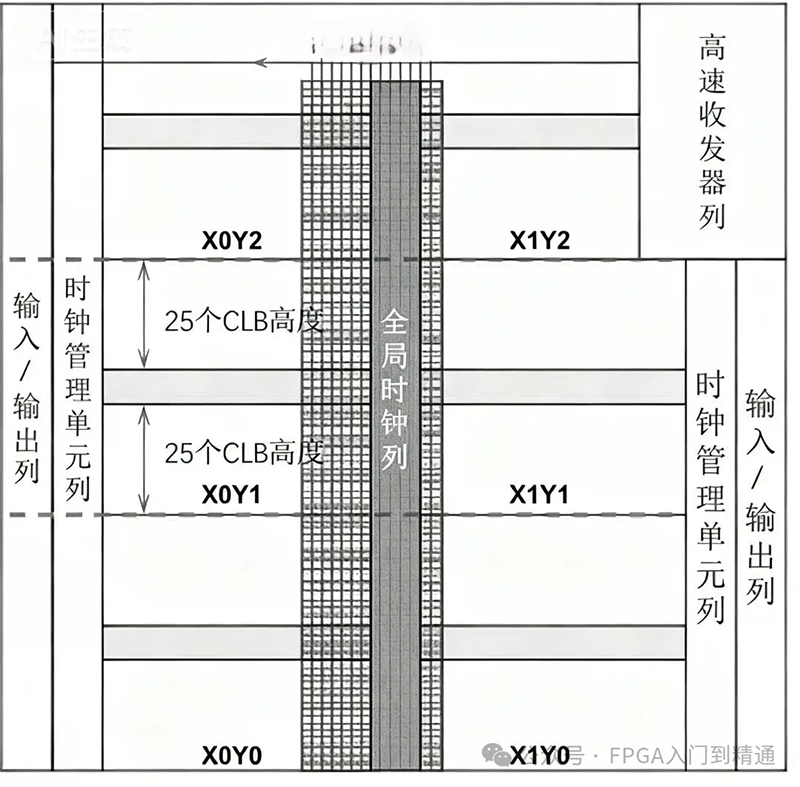

2、7系列FPGA有多少个全局时钟缓冲器?

7系列FPGA有32个全局时钟缓冲器。

这32个全局时钟缓冲器位于全局时钟列,不属于任何时钟区域(Clock Region)。

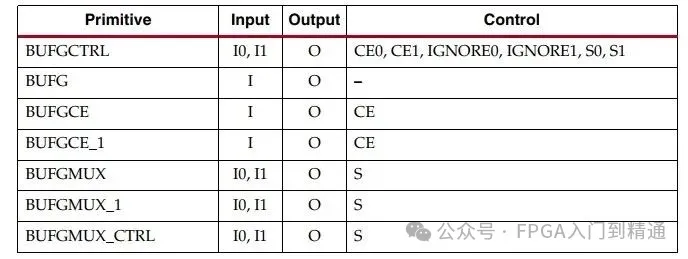

3、全局时钟缓冲器的例化原语有哪些?

全局时钟可例化的原语有7种,输入输出端口区别如下表。

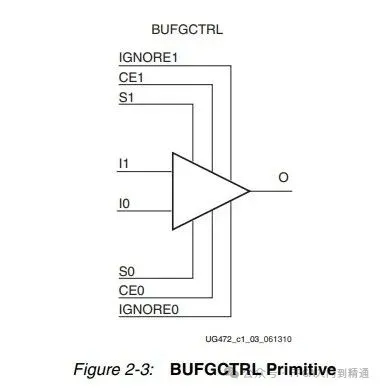

BUFGCTRL原语可以用于切换两个异步时钟。

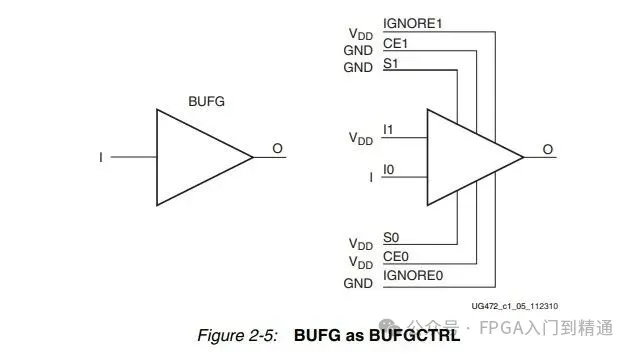

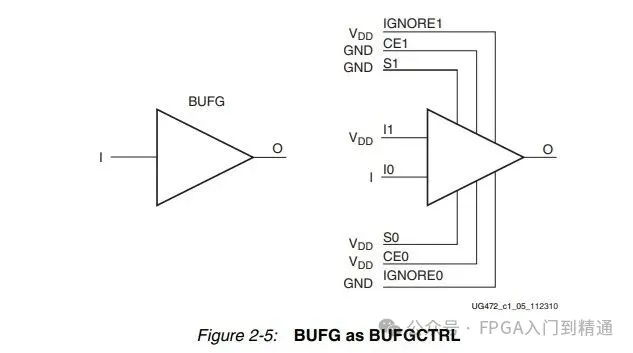

如下图所示,I0和I1是两个时钟输入端口,而S0、S1、CE0、CE1、IGNORE0、IGNORE1是相应的控制信号,O是输出时钟端口。

原语:

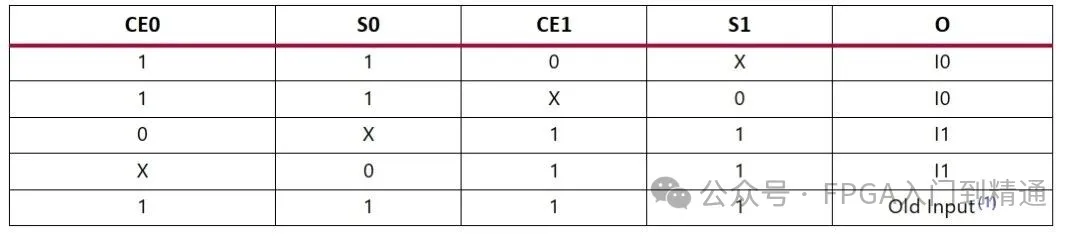

BUFGCTRL #( .INIT_OUT(0), // 初始输出电平(0/1) .PRESELECT_I0("TRUE"), // 上电默认选择I0 .PRESELECT_I1("FALSE") // 上电默认选择I1) u_bufgctrl ( .O(clk_out), .CE0(1'b1), // I0使能 .CE1(1'b1), // I1使能 .I0(clk0), .I1(clk1), .IGNORE0(1'b0), // 不忽略I0检测 .IGNORE1(1'b0), // 不忽略I1检测 .S0(sel0), // 同步选择 .S1(sel1));真值表:

(2)BUFG

BUFG是一个时钟缓冲器,有一个时钟输入和一个时钟输出。此原语也是基于BUFGCTRL。

原语:

BUFG u_bufg_clk ( .I(clk_in), // 输入时钟 .O(clk_out) // 输出全局时钟);

(3)BUFGCE和BUFGCE_1

带使能功能的全局时钟缓冲器,可以看作是 BUFG 的一个增强版,增加了一个时钟门控功能。

核心功能是:在使能信号 CE 为高电平时,将输入时钟 I 传递到输出 O;当 CE 为低电平时,输出 O 保持为低电平。

原语:

BUFGCE u_bufgce_clk ( .I (clk_in), // 时钟输入 .CE(ce), // 高有效使能 .O (clk_out) // 门控时钟输出);

BUFGCE_1 u_bufgce_1_clk ( .I (clk_in), // 时钟输入 .CE(ce_n), // 低有效使能(输入ce_n为0时,时钟输出有效) .O (clk_out) // 门控时钟输出);

二、区域缓冲器

区域缓冲器也称为局部缓冲器,包括BUFH、BUFIO、BUFR和 BUFMR等等。

1、为什么叫区域缓冲器?

这是因为它们输出的时钟经区域时钟树(Regional Clock Tree)之后可到达特定时钟区域内的逻辑时钟端口。

区域缓冲器隶属于时钟区域(Clock Region)。

每个时钟区域包括12个BUFH、4个BUFIO、4个BUFR和2个BUFMR。

2、时钟区域(Clock Region)如何理解?

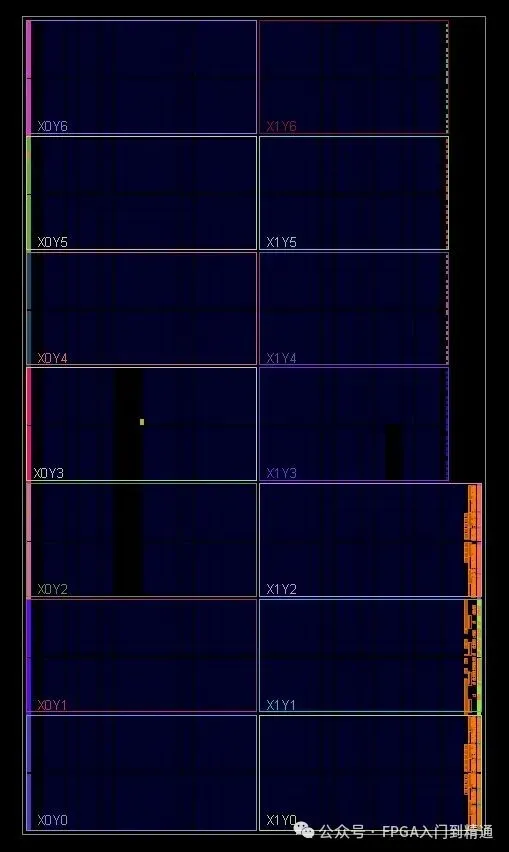

时钟区域是FPGA芯片内部的一个物理和逻辑上的划分区域。

每个区域包含一定数量的逻辑资源(如CLB、BRAM、DSP等)、输入输出接口以及专用的时钟路由和缓冲资源。

可以通过在Vivado或Quartus的Device视图中查看芯片的布局图来直观地看到它们,通常是纵横交错的网格。

其中XmYn是时钟区域坐标。

3、局部时钟缓冲器的例化原语有哪些?

(1)BUFH/BUFHCE

BUFH/BUFHCE是水平时钟缓冲器,全局时钟线可以通过它们进入到单个的时钟区域。

BUFH的输入时钟可以是来自同一时钟区域或相邻水平时钟区域内的 MRCC 、 SRCC 、 CMT 、 BUFG 或高速收发器的输出时钟

RXOUTCLK/TXOUTCLK。

如下图所示,时钟区域X1Y0的BUFH可由本区域内的MRCC驱动,也可由X0Y0内的MRCC驱动,这就是相邻水平时钟域的概念。

BUFH的输出可连接到CMT的时钟端口或同一时钟区域内BUFG可到达的时钟端口。

(2)BUFIO

BUFIO是I/O时钟缓冲器,每个I/O时钟缓冲器可以驱动I/O时钟树,I/O时钟树可以让时钟不断地进入该I/O bank内的I/O资源。在每个区域中,有4个独有的I/O时钟可以驱动该区域的I/O bank。

BUFIO输入时钟可以是同一时钟区域内的MRCC、SRCC、MMCM的输出时钟CLKOUT0~CLKOUT3、MMCM的输出反馈时钟CLKFBOUT或BUFMR。

BUFIO的输出时钟只能驱动ILOGIC和OLOGIC。

(3)BUFR

BUFR是区域时钟缓冲器。

BUFR的输入时钟和BUFIO一样。

但BUFR的输出时钟可驱动CMT和同一时钟区域的逻辑资源ILOGIC和OLOGIC。