文章来源:FPGA开源工作室

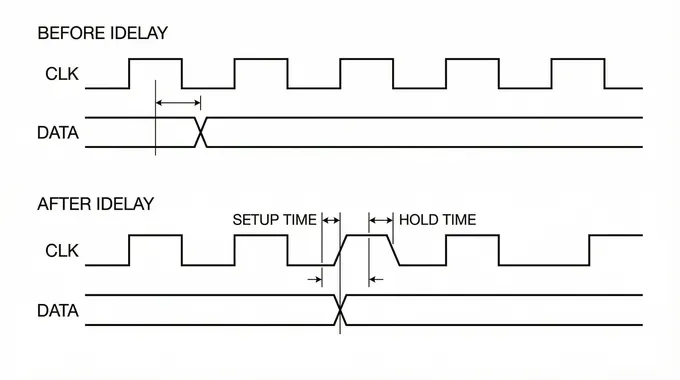

在高速接口设计中,时序收敛往往是工程师面临的最大“噩梦”。当数据传输速率突破 800Mbps 时,微小的 PCB 走线差异都足以让系统崩溃。本文将深度剖析 Xilinx 7 系列(IDELAYE2)与 UltraScale 系列(IDELAYE3)的底层原理,带你彻底攻克输入延迟校准难题。

一、核心基础概念:为什么我们需要 IDELAY?

在高速系统中,信号在 PCB 上的传播速度约为 6英寸/ns。这意味着 100mil 的走线误差约等于 16ps 的时间偏差。在 DDR3-1600 中,一个数据窗口仅有 625ps。如果 PCB 绕线无法做到绝对等长,数据眼图就会闭合。

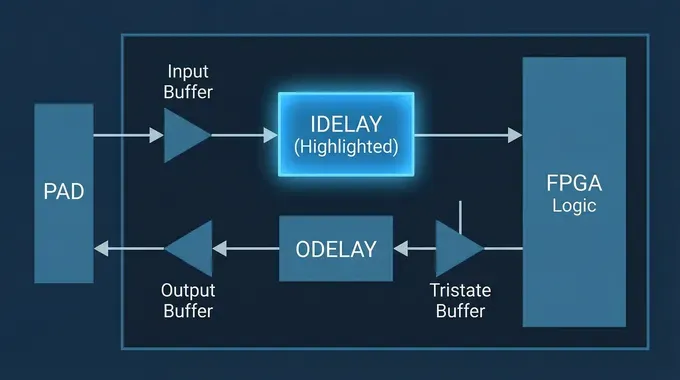

IDELAY 的作用,就是位于 FPGA IO Pad(焊盘)与内部逻辑之间,通过精确控制延时链(Delay Line),在亚纳秒级别“微调”输入信号的到达时间。设计时需牢记以下三大铁律:

物理位置锁定:

IDELAY 位于 IOB 内部,紧邻物理引脚。一旦信号进入内部布线,无法再使用。

伴侣关系:

在 DDR 等应用中,必须与 ISERDES 级联使用。

心脏依赖:

必须由 IDELAYCTRL 提供高精度参考时钟,否则无法保证延时准确性。

二、IDELAYE2 详解(7 系列 FPGA)

对于 Artix-7, Kintex-7, Virtex-7,IDELAYE2 是主力军。它采用“抽头(Tap)”式结构,共有 32 个 Tap,每个 Tap 平均延时约 78ps(受参考时钟影响),总延时范围 0 ~ 2.5ns。

标准动态可调模式(VARIABLE)例化代码:

IDELAYE2 #(

.CINVCTRL_SEL ("FALSE"),

.DELAY_SRC ("IDATAIN"), // 关键:信号源来自IOB引脚

.HIGH_PERFORMANCE_MODE ("TRUE"), // 开启高性能模式减少抖动

.IDELAY_TYPE ("VARIABLE"), // 动态可调模式

.IDELAY_VALUE (0),

.REFCLK_FREQUENCY (200.0), // 参考时钟需与IDELAYCTRL一致

.SIGNAL_PATTERN ("DATA")

)

idelay_inst (

.CNTVALUEOUT (cntvalueout), // 输出当前延迟值(调试神器)

.DATAOUT (dataout), // 输出至ISERDES

.C (clk),

.CE (ce), // 1=使能调整

.IDATAIN (datain), // 来自物理Pad的输入

.INC (inc), // 1=增加延迟,0=减少

.LD (1'b0),

.REGRST (rst)

);

三、IDELAYE3 详解(UltraScale/UltraScale+ 系列)

在 UltraScale 架构中,E3 带来了质的飞跃:

精度革命:

原生精度提升至 4~10ps,适应 DDR4-2400+。

Native Time Mode:

支持 DELAY_FORMAT = "TIME",可直接设定 500ps,无需手动计算 Tap。

VT 自动校准 (EN_VTC):

FPGA 后台自动补偿电压温度漂移,保证延时绝对稳定。

UltraScale IDELAYE3 例化代码:

IDELAYE3 #(

.DELAY_FORMAT ("TIME"), // 【亮点】单位直接使用ps

.DELAY_TYPE ("VARIABLE"),

.DELAY_VALUE (100), // 初始延迟 100ps

.REFCLK_FREQUENCY (300.0), // 推荐参考时钟300MHz

.UPDATE_MODE ("ASYNC")

)

idelay_inst (

.CNTVALUEOUT (cntvalueout),

.DATAOUT (dataout),

.CE (ce),

.CLK (clk),

.DATAIN (datain),

.EN_VTC (en_vtc), // 【核心】使能自动补偿

.INC (inc),

.RST (rst) // 注意:E3是RST,E2是REGRST

);

四、IDELAYE2 vs IDELAYE3 全面对比

五、工程实战应用案例

案例 1:DDR3 接口物理层(IDELAYE2 + ISERDES)

核心逻辑是“盲调”。FPGA 通过状态机扫描 0~31 个 Tap,找到数据最稳定的点。注意由于 PCB 走线差异,每一位数据(DQ)必须独立例化 IDELAY。

genvar i;

generate

for(i = 0; i < 8; i = i + 1) begin : gen_delay

IDELAYE2 #(

.IDELAY_TYPE ("VARIABLE"),

// ... (其他参数) ...

) idelay_dq (

.IDATAIN (dq_in[i]), // 每一位独立输入

.DATAOUT (dq_delayed[i]),

.INC (delay_inc),

.CE (delay_ce),

// ...

);

ISERDESE2 #( .DATA_RATE("DDR"), .DATA_WIDTH(8) ) iserdes_dq (

.D (dq_delayed[i]), // 接收经过延时校准的数据

// ...

);

end

endgenerate

案例 2:MIPI D-PHY 接口(IDELAYE3)

利用 E3 的高精度和 VAR_LOAD 模式实现快速对齐。

IDELAYE3 #(

.DELAY_FORMAT ("TIME"),

.DELAY_TYPE ("VAR_LOAD"), // 允许直接加载数值

.DELAY_VALUE (50), // 初始补个 50ps 的 PCB 差异

.REFCLK_FREQUENCY (300.0),

.UPDATE_MODE ("ASYNC")

) idelay_mipi (

.DATAOUT (data_delayed),

.EN_VTC (1'b1), // 保持高电平,让FPGA自动抵抗温漂

.LOAD (load_delay),

.CNTVALUEIN (optimal_delay_val) // 直接加载算法值

);

六、使用必备注意事项

1. IDELAYCTRL 是必须的! 一个 I/O Bank 内的所有 IDELAY 共享该 Bank 对应的 IDELAYCTRL。系统上电后,必须先复位 IDELAYCTRL,等待其 RDY 信号拉高。

2. 时钟驱动有洁癖: IDELAY 的参考时钟严禁使用普通逻辑时钟,必须使用 BUFG/BUFIO 产生的稳定时钟。

3. 多通道独立性: 不要试图用一个 IDELAY 控制一组总线。8 位数据线必须例化 8 个 IDELAY。

总结: IDELAY 原语是 FPGA 通往高速世界的“门票”。7 系列 (E2) 稳健经典,适合 DDR3;UltraScale (E3) 引入皮秒级 Time 模式和自动温补,是 DDR4 和 MIPI 的不二之选。