高性能SoC芯片设计中,高速接口类的相关设计(如PCIe4/5、以太网100G/200G、MIPI、DDR4/5等)在FPGA原型验证或硬件仿真验证平台上,运行速度一般只有几十兆级别,与这些实际高速接口真实运行速率差距较大,故而无法直接连接外部相关高速外设,因此我们设计相应的降速桥(Speed Bridge 或Speed Adaptor)进行数据速率适配。简单来说,降速桥主要应用于需要高速数据传输或设备间通信速率协调,以验证其相关控制逻辑功能的正确性,常见于原型验证(Prototyping)与硬件仿真加速器(Emulator)验证平台,加快SoC芯片系统功能验证进程。降速桥通过协调高速与低速设备间的通信,保证SoC芯片流片前高速接口IP相关数据传输与芯片实际应用环境尽量一致,确保高速接口相关IP设计与外部设备间的数据传输正确与稳定,以达到SoC芯片流片前系统功能验证的完备,从而降低芯片流片失败风险。

降速桥种类较多,如PCIe降速桥、以太网降速桥、MIPI降速桥等。本文主要介绍亚科鸿禹PCIe Gen5降速桥的原理及特点。

1. PCIe降速桥原理

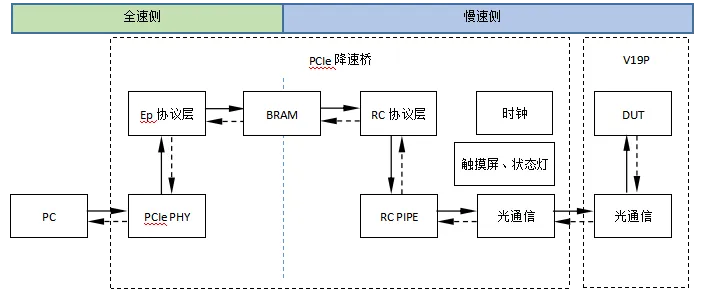

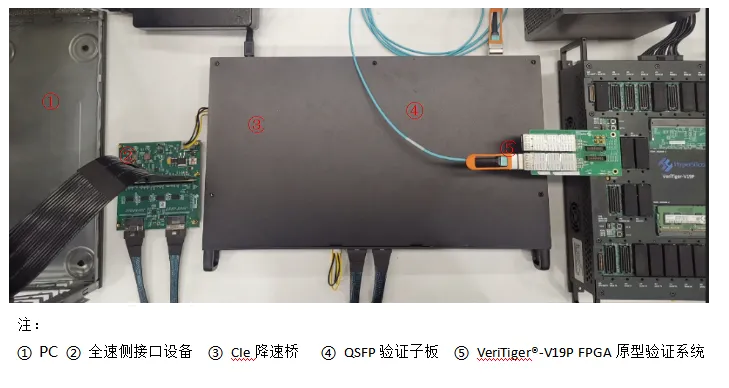

图2 所示为亚科鸿禹设计的PCIe降速桥产品在实际应用中的系统连接图,其中PCIe PHY参考时钟、光通信模块参考时钟、慢速侧PIPE数据时钟、状态灯驱动时钟等均有一个时钟模块来产生;LCD触摸屏用于设置系统模式、慢速侧PCIe速度、lanes、PIPE时钟频率及显示系统状态信息等;状态灯用于显示全速侧和慢速侧建链状态。

2. PCIe降速桥系统特点

亚科鸿禹降速桥介绍

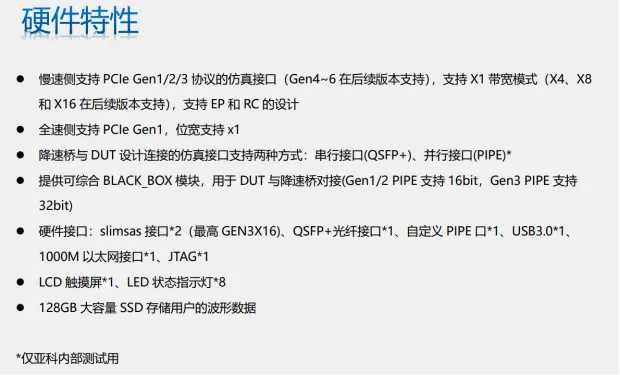

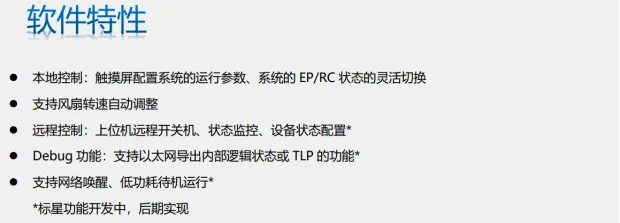

HSADP-PCIE100是搭载亚科鸿禹自研IP的PCIe Gen5降速桥,可与亚科鸿禹的原型验证平台或者仿真加速器协同,实现 PCIe Gen5 接口的DUT设计相关功能以及协议一致性的验证工作。

文章来源:亚科鸿禹