作者:赵瑜斌Robin,来源:IC后摩号

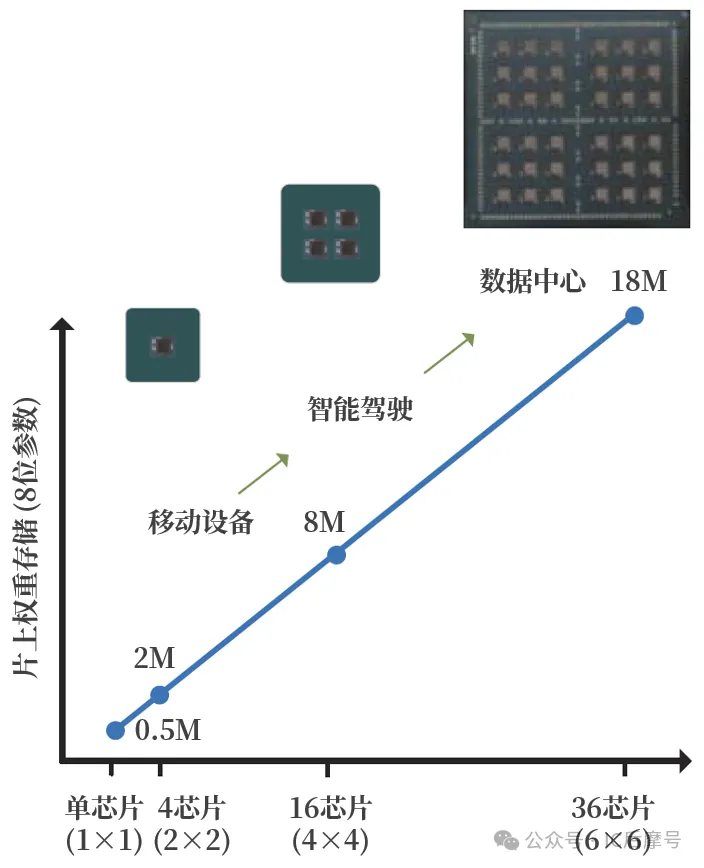

在一项坦福、麻省理工和英伟达的多芯片模块研究中,通过地参考信号生成以网格网络连接的36个芯粒组成的深度神经网络加速器,其架构显示出灵活扩展性,适用从移动端到数据中心领域的各种深度神经网络,实现高效的推理。

Content

深度神经网络需求

神经网络加速器

推理加速器架构

高效多芯片推理模式

结果分析

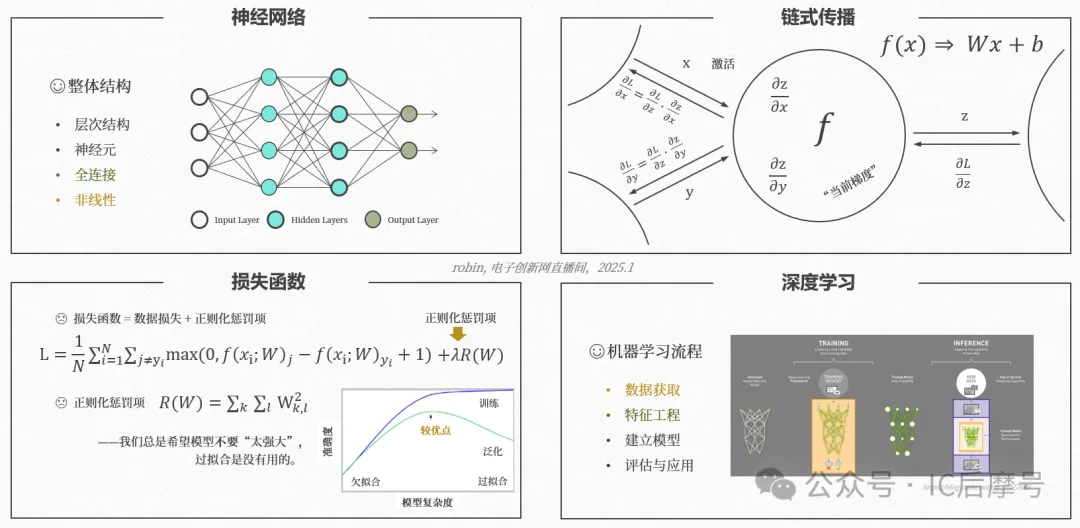

深度神经网络由一系列层构成,包括卷积层、池化层、激活层和全连接层。

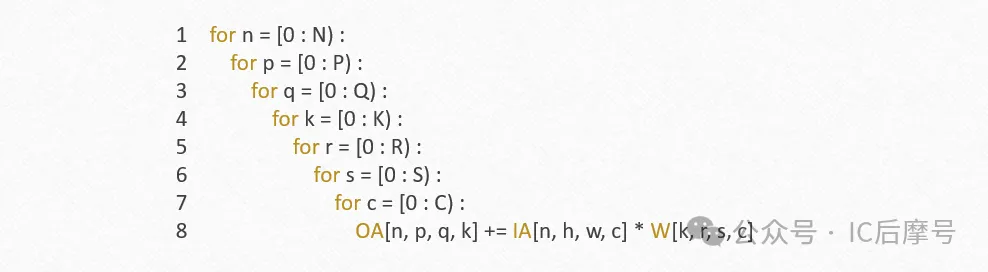

卷积层在算法上被公式化为对输入激活张量、权重张量和输出激活张量的七维嵌套循环,下图展示其卷积计算。

同样的公式也适用于多层感知机和循环神经网络中广泛使用的全连接层。激活层应用非线性函数,如ReLU或sigmoid,而池化层在卷积层之后对输入激活进行下采样。激活层和池化层在执行期间通常与卷积层合并,以减少数据移动。

深度神经网络具有多样化的性能、精度和功耗目标。然而,由于高昂的设计和制造成本,为每个目标构建专用加速器不可行。

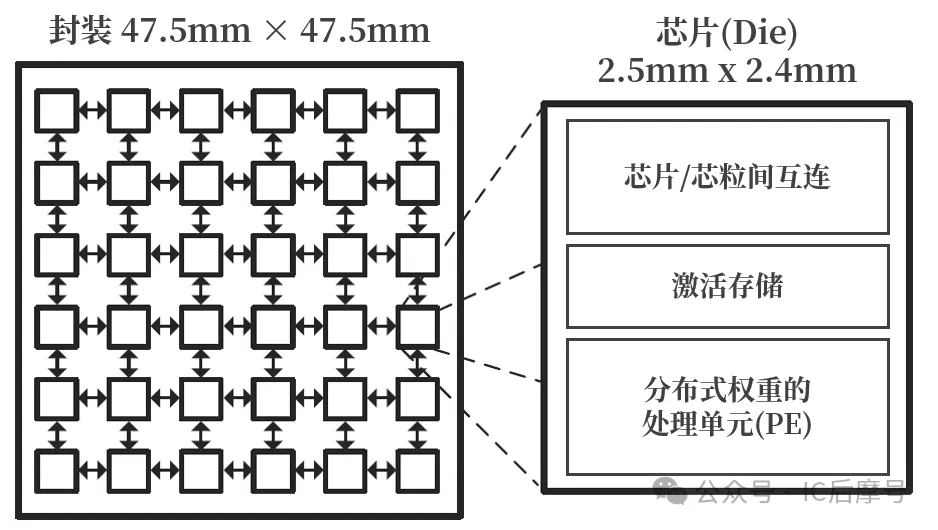

架构设计考虑利用低能耗、高带宽的芯片间通信链路,从单个推理加速器芯片(芯粒)组装具有不同计算能力的系统。通过由分组交换片上网络(NoC)和封装内网络(NoP)路由器连接的分布式基于瓦片的架构,支持处理单元灵活且高效的扩展。

2. 可扩展神经网络加速器

同一芯片(裸die)封装在有机基板上构成单芯片、4芯片和36芯片系统。深度神经网络权重被静态地平铺在片上存储器中,支持存储50万至1800万个8位权重,并为1至36芯片系统提供4至128 TOPS的峰值性能。

地参考信号收发器用于芯片间通信。可扩展性本身不受封装尺寸的限制,因为这些收发器也可以在PCB上多个封装之间进行短距离通信。

同样的模块方法、模块架构可实现不同规模的系统。

3. 推理加速器架构

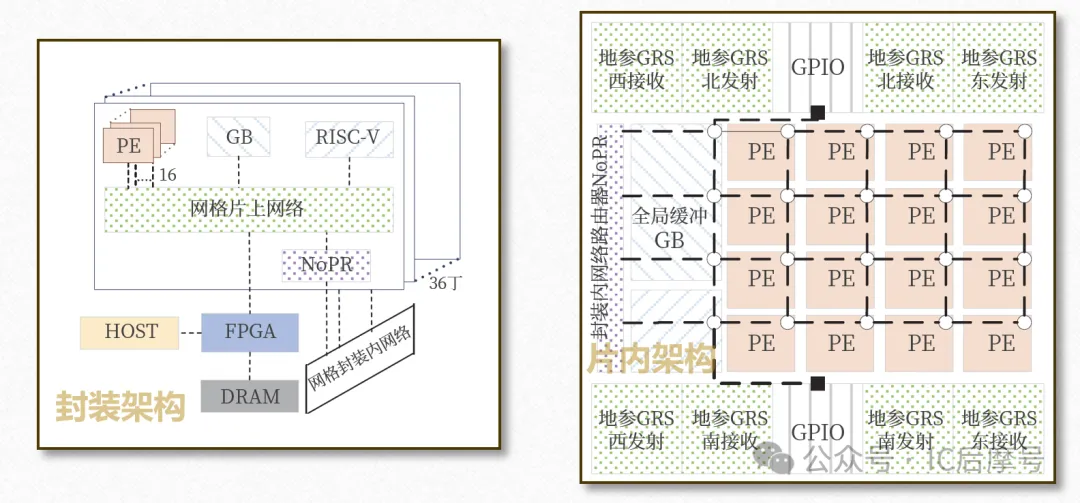

在封装上集成36个芯片,通过网格拓扑连接。每个die包含一个封装内网络(NoP)路由器、一个全局缓冲器(GB)、一个RISC-V控制处理器,以及通过具有64位宽路由器的网格化片上网络(NoP)连接的16个处理单元。

封装内网络路由器通过地参考信号收发器在片上网络和相邻芯片之间传输数据包。全局缓冲器包含一个64KB的统一缓冲器,作为激活值的二级存储。处理单元执行卷积层、全连接层以及偏置加法、ReLU和池化等后处理功能。

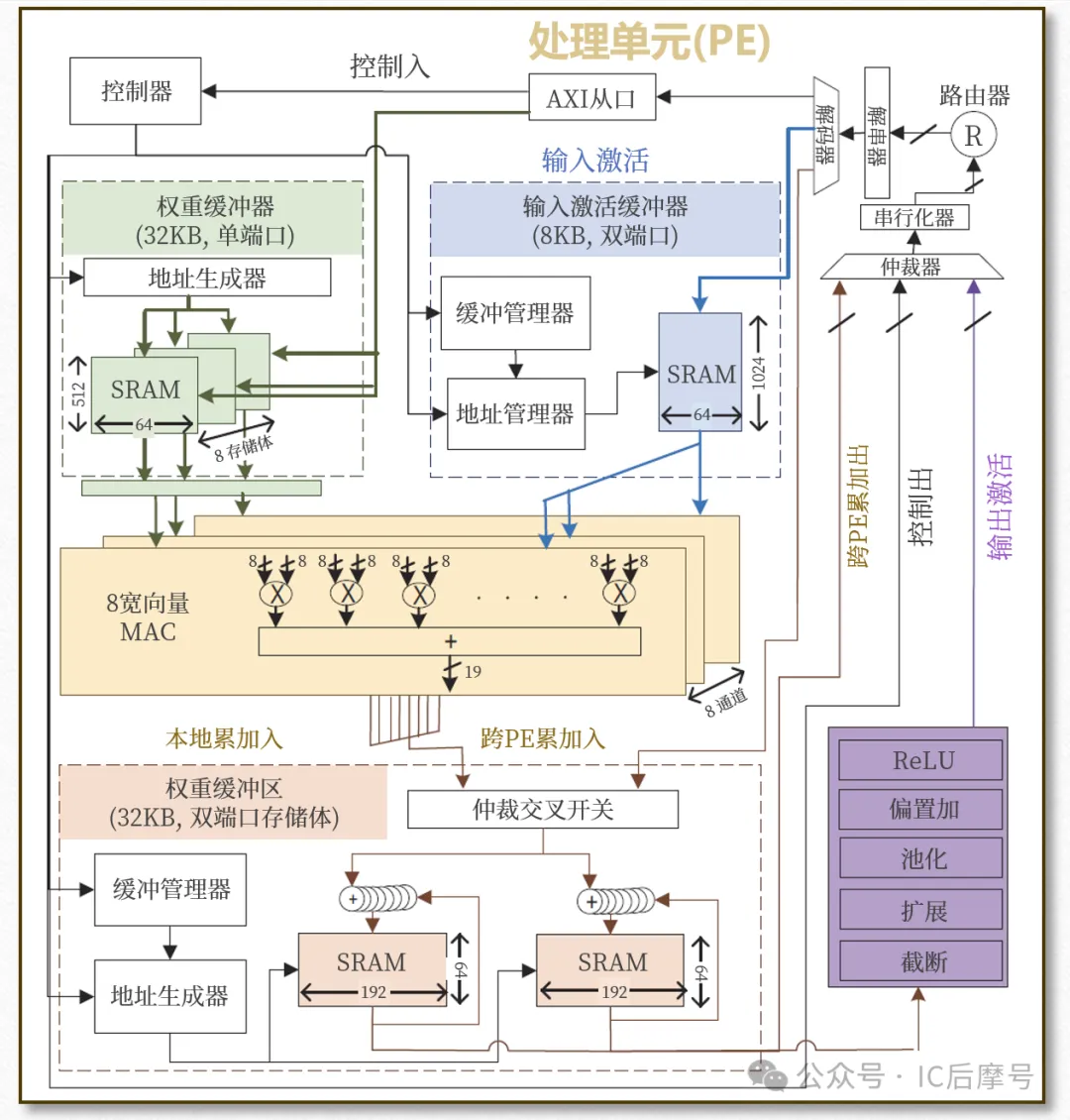

每个处理单元包括一个8KB输入缓冲器、一个32KB权重缓冲器和一个3KB累加缓冲器。大的权重缓冲器支持持久化权重存储,以最小化DRAM流量。输入激活在8条并行向量乘累加单元通道上进行空间重用,而权重则进行时间重用。

每个向量MAC执行8路点积,并每个周期将部分和累加到累加缓冲器中。选择8位定点精度用于权重和激活,以及24位累加精度,以优化能效而不损失精度。

该架构包含通过片上网络和封装内网络连接的分布式处理单元和全局缓冲器

4. 高效多芯片推理模式

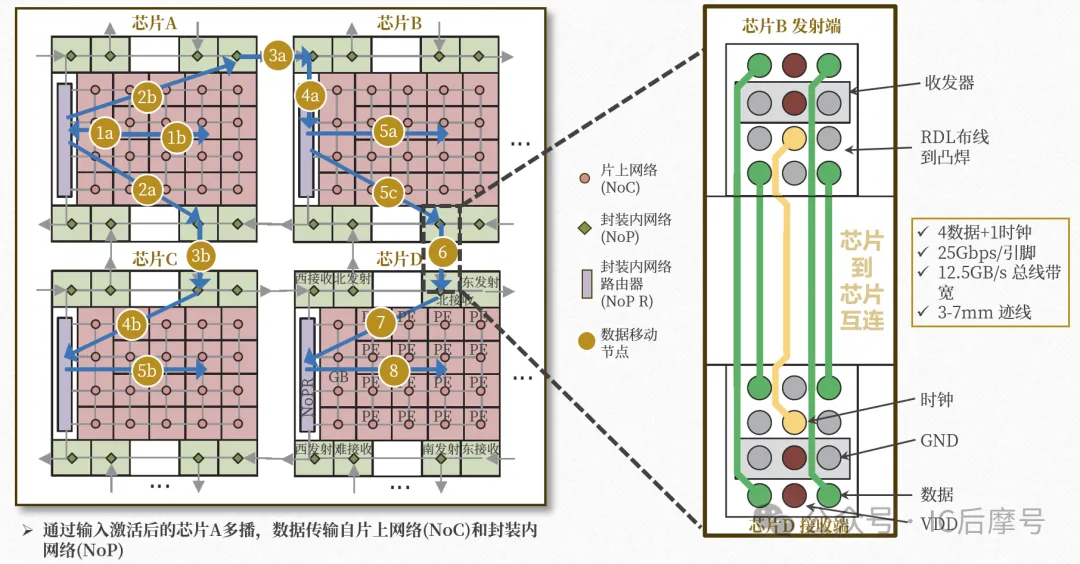

通过多播操作。输入激活通过片上网络和封装内网络从一个芯片的全局缓冲器发送到其他芯片的处理单元。芯片的IO区域包含8个芯片间地参考信号收发器宏,其中4个配置为接收器,4个配置为发送器。

每个收发器宏有4个数据通道和一个时钟通道,可配置速度从11Gbps/引脚到25Gbps/引脚,功耗为0.82-1.75 pJ/bit,面积为0.26mm²,总峰值芯片带宽为800Gbps,峰值带宽密度为384Gbps/mm²。

地参考信号相对同期的多芯片模块案例在单位芯片面积上的带宽提高了约3.5×,每比特能耗更低。在25Gbps速率下,眼图张开度为0.7UI。

通过在不同芯片和处理单元之间对计算进行空间平铺是另一个关键技术,利用深度神经网络中的并行性和数据重用,从而最大化MAC利用率并最小化通信功耗。

RISC-V控制核心通过软件管理的寄存器配置处理单元和全局缓冲器之间的通信。在封装级:

1) 权重沿输入通道维度和输出通道维度在不同芯片之间分割;

2) 输入激活沿具有匹配C维度的芯片行进行多播;

3) 输出激活沿芯片列进行归约。在芯片级,权重类似地沿C和K维度平铺,而输入激活通过片上网络进行多播。对于输入或输出通道较少的层,也支持其他平铺选项。在处理单元级,权重在处理输入图像时从权重缓冲器加载一次(权重固定数据流)。

5.结果分析

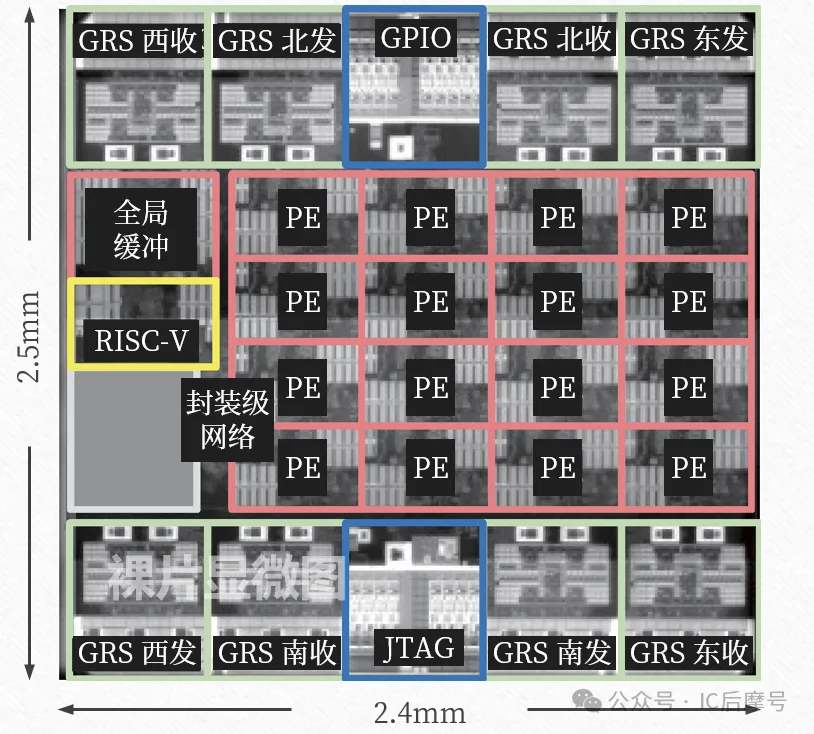

通过以上技术集成的多芯片模块:6mm²理加速器采用台积电16nm FinFET工艺制造。

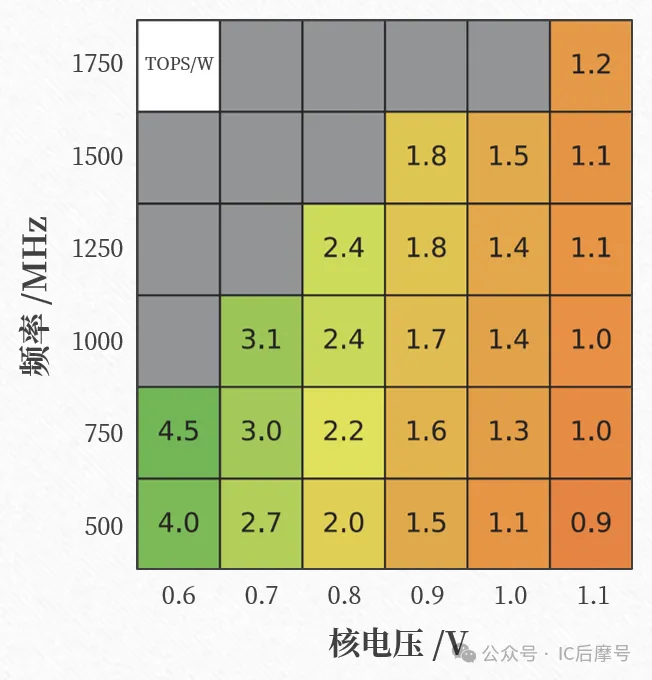

不同电压下36芯片核心的能效表现,系统能效随电压变化如下图。

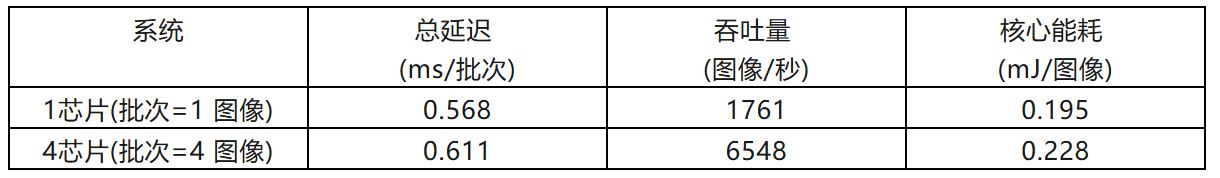

在一款用于自动驾驶汽车的端到端深度神经网络框架DriveNet中,汽车级系统的测量性能发现:功耗和性能测量在权重加载到每个处理单元的权重SRAM且输入加载到全局缓冲器之后开始。

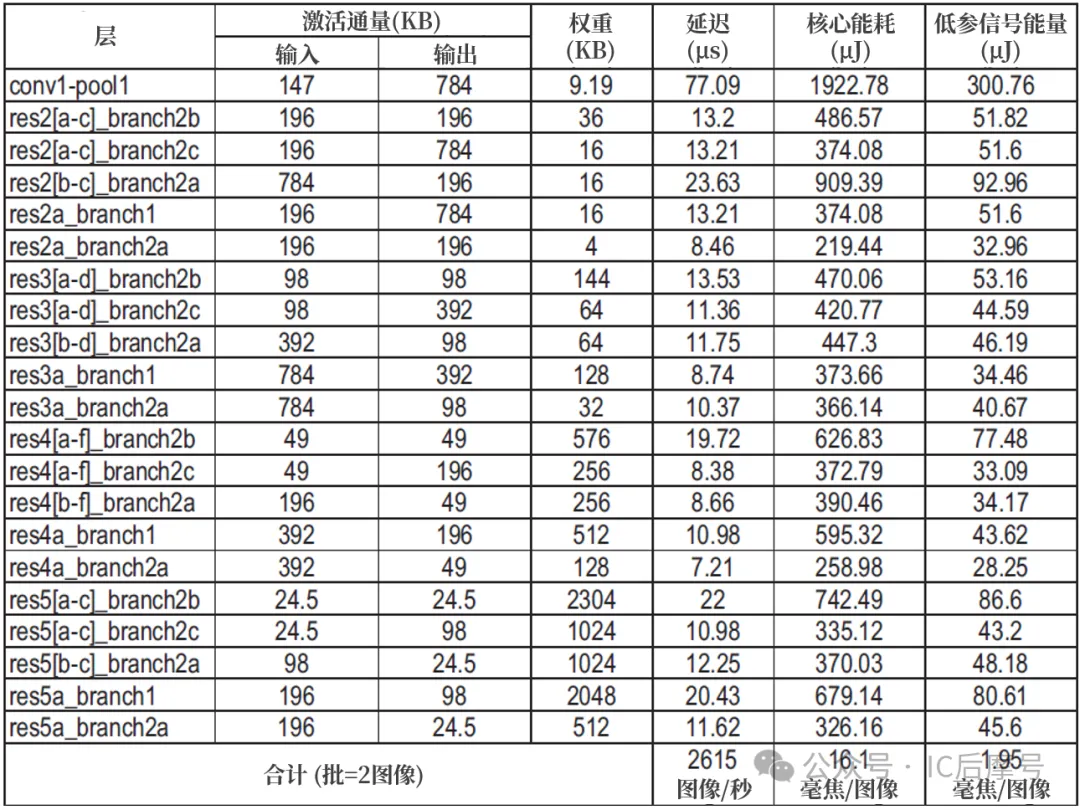

该架构具有扩展性,运行ResNet-50每一层的36芯片数据中心级(HPC)系统的测量性能。系统在0.85V标称电压下达到2615图像/秒。

参考文献

1. Brian Zimmer, A 0.11 pJ/Op, 0.32-128 TOPS, Scalable Multi-Chip-Module-based Deep Neural Network Accelerator with Ground-Reference Signaling in 16nm, 2019 Symposium on VLSI Circuits Digest of Tech Papers.