作者:赵瑜斌Robin,来源:IC后摩号

随着芯片到芯片中介层和驱动器技术的日益成熟,开发独立的系统级IP已经箭在弦上:针对DNN加速器,或者专用于LLM训练的AI芯片开发可进行芯粒化设计。本文的设计范例,由一个CPU和两个机器学习加速器组成,采用仿真的芯粒配置,并使用高级接口总线(AIB)进行连接。

Content

1 接口设计

D2D互连方案

AIB应用

系统架构

整体架构与扩展接口

CPU

稀疏CNN加速器

长短期记忆网络加速器

结果仿真

版图、仿真、测试向量

小结

接口设计

从架构层面组合芯粒,一种方法是围绕IP模块进行固化可使IP被冻结,便于独立验证,并将设计问题限制在封装和互连层面——这种方法将验证从设计阶段转移到封装阶段,很大程度上压缩了SoC设计链,并且减少了过设计。同时,其存在的挑战是验证框架,以及需要更多实例来验证该方法。

芯粒互连技术在芯粒生态系统中至关重要。传统的片外通信方法依赖于高度串行化的事务处理。然而,芯片到芯片的互连方案采用了不同的方法:利用短距离链路所允许的低损耗信道和高密度优势。同时,具有低电压摆幅的并行总线同时被采用,以实现高带宽传输中的最小化功耗。

用于高密度、高带宽和低功耗通信的芯片到芯片互连方案已被广泛开发,下表展示流行接口性能和边缘密度的指标。

每边缘带宽密度的领先者是MDIO,XSR/USR具有最高的每通道吞吐量,而UCIe具有最小的延迟和最低的物理层每比特能耗。

在美丽国国防高级研究计划局(DARPA)从英特尔公司获得了AIB作为足够成熟的芯粒的免版税互连标准。使用AIB进行D2D通信为该AI芯粒组合与英特尔现场可编程门阵列(FPGA)集成创造了机会,展示了AI芯粒设计套件的可用性和AIB的灵活性。

系统架构

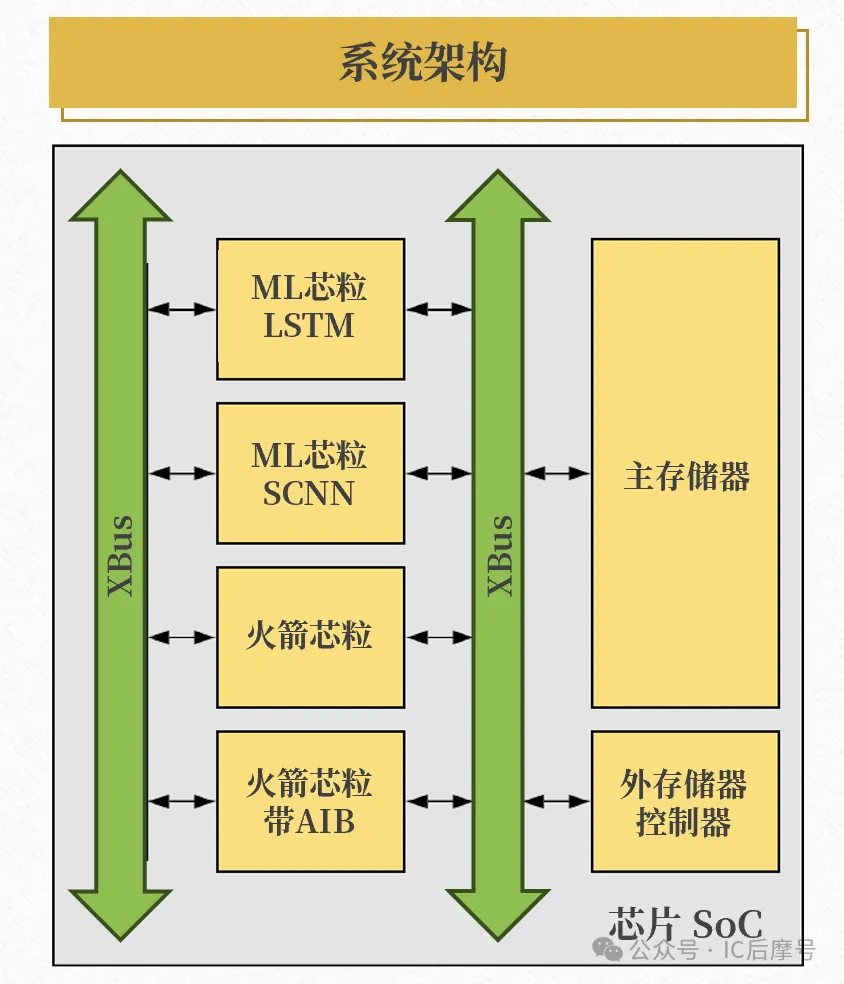

系统架构包括一个芯粒组合,该组合包含5个不同类型的芯粒,置于一个仿真的2.5D结构上,下图为完整系统的模块级框图。包括两个机器学习芯粒、两个CPU、片上静态随机存取存储器(SRAM)以及一个片外存储器控制器。

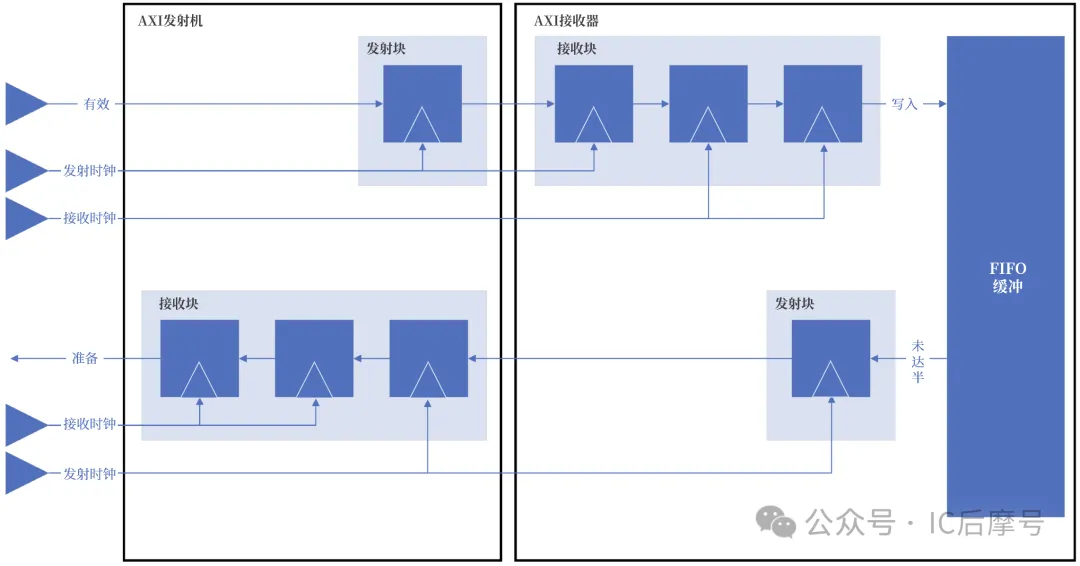

芯粒通信协议由三层协议栈组成:物理层是AIB,通信协议是高级可扩展接口(AXI),还有一组先进先出(FIFO)缓冲区来处理跨越AIB物理层的延迟。

系统的片上网络(NoC)由一组采用交叉开关配置的AXI总线组成。主存储器总线(MBus)将片上/片外存储器连接到CPU和机器学习芯粒。控制存储器总线(XBus)将CPU连接到机器学习芯粒。

每个芯粒都有一个外部联合测试行动组(JTAG)编程接口。片外存储器接口是芯粒协议接口(CPI)的一个变种。仿真的2.5D结构位于其中一个CPU芯粒上,所有其他芯粒仅使用协议栈的AXI部分。

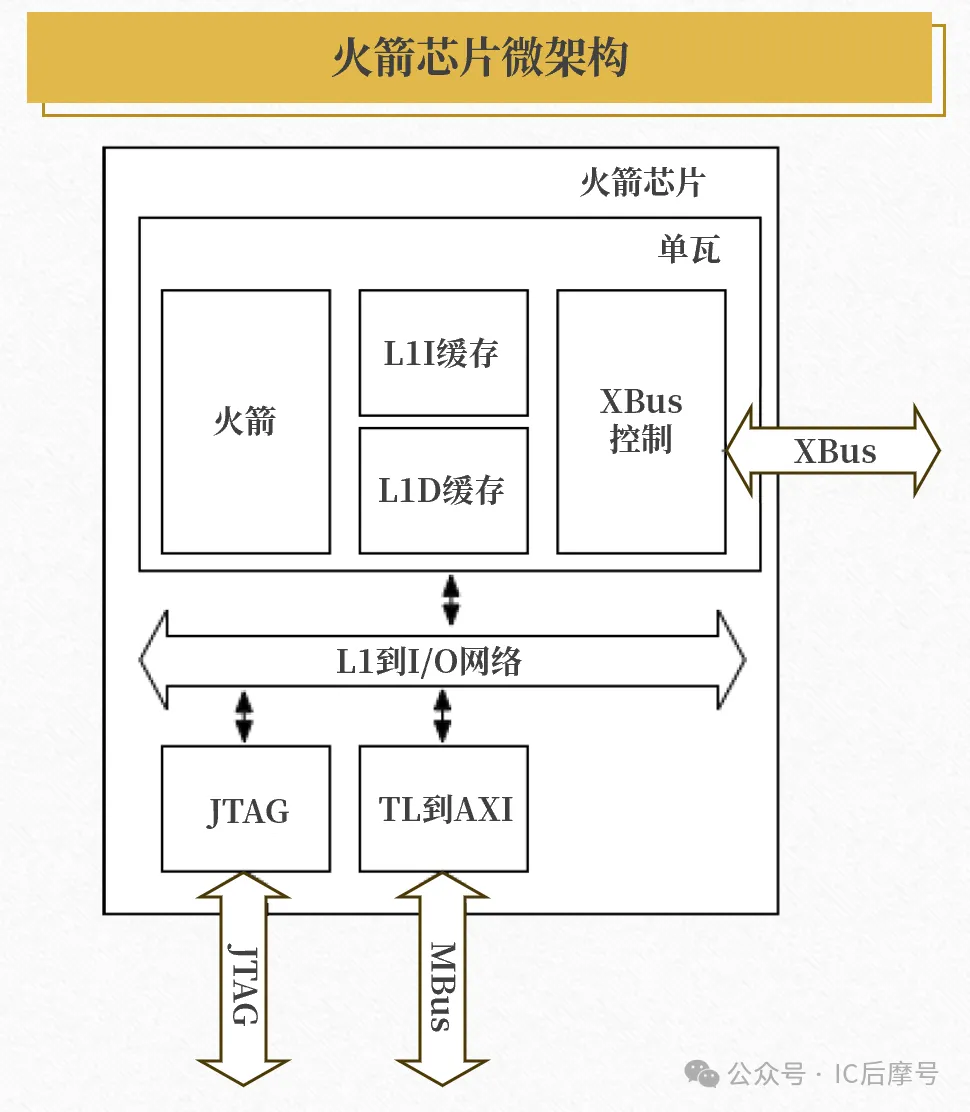

A. CPU(火箭芯片)

本设计中使用一款定制的“火箭芯片”CPU,是一个单取指、单发射、顺序执行的标量处理器。下图展示该定制生成的“火箭芯片”的系统架构。

CPU支持与机器学习加速器接口的自定义扩展指令,以及用于预处理和通用处理的多种ISA扩展(IMAFD)。

CPU的主要作用是为机器学习加速器提供一个真实的编程接口,次要作用是执行预处理任务。CPU通过XBus与机器学习加速器通信。

XBus是专用于发送和接收命令的总线,并支持发送少量数据。XBus的存储器控制器使用指令集架构(ISA)的自定义扩展指令之一作为总线读/写命令。这些总线命令为读取和设置内存映射寄存器提供了一个编程接口。这些寄存器的布局取决于具体的芯粒。

B. 稀疏CNN(SCNN)加速器

SCNN利用了特征和参数中的不规则稀疏性,仅对非零元素进行计算,从而带来显著的算力提升。该架构包含一种跳零技术,将每个输入特征行编码为游程长度压缩(RLC)格式。这成功地仅向处理单元(PE)传递非零输入特征,通过跳过零特征来最大化处理单元利用率。

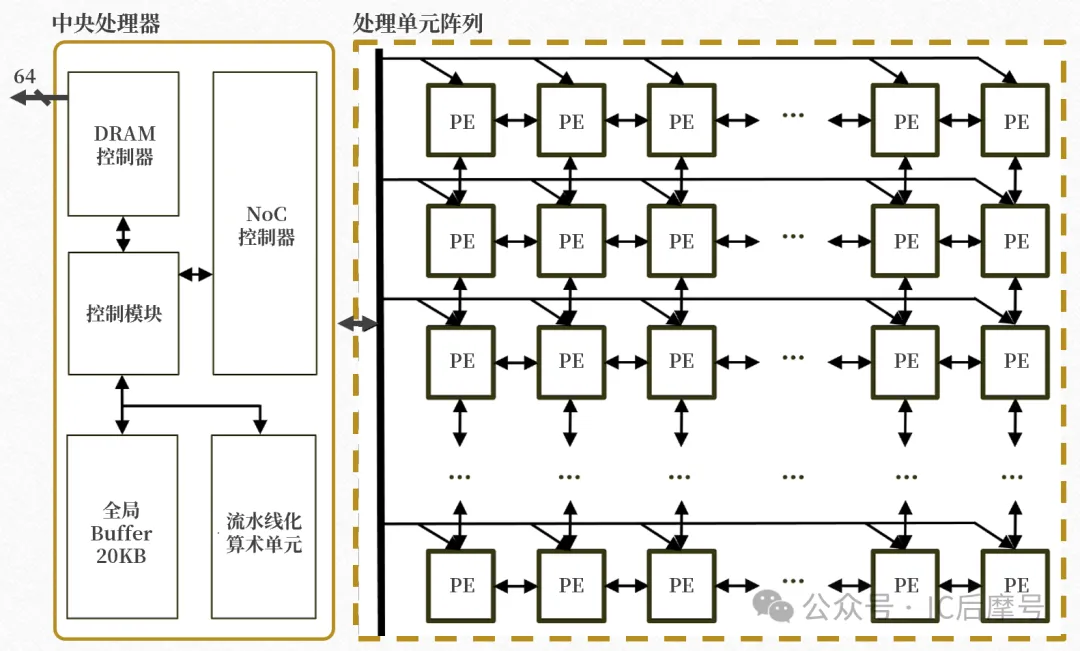

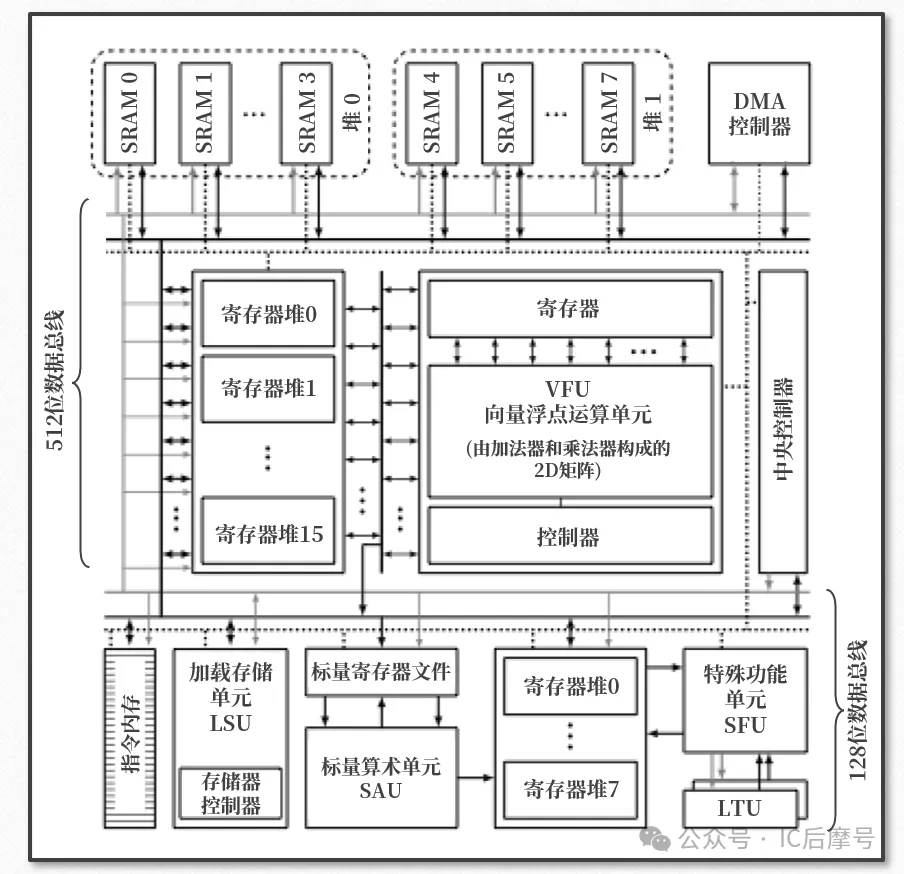

SCNN加速器包括一个专用指令集处理器(ASIP),该处理器包含一个中央处理器和一个PE阵列,微架构如下图。

中央处理器负责同步来自存储器的数据与相应的PE。PE阵列由4x4个PE组成,每个PE通过一个网格网络连接到4个相邻的PE。PE执行所需的算术计算以最大化PE利用率。

C. 长短期记忆(LSTM)网络加速器

LSTM芯粒是一个可扩展、可配置的ASIP。该ASIP的ISA同时支持训练和推理。该架构通过采用片上SRAM组来解决预取挑战:在对当前数据集执行计算的同时,存储下一组计算的数据。

LSTM架构包含128个PE。每个PE执行整个网络的一个子集。PE内部的直接内存访问(DMA)是完全可编程的,负责处理混合精度训练,并为反向传播以相反顺序访问权重。下图展示其系统微架构。

结果与仿真

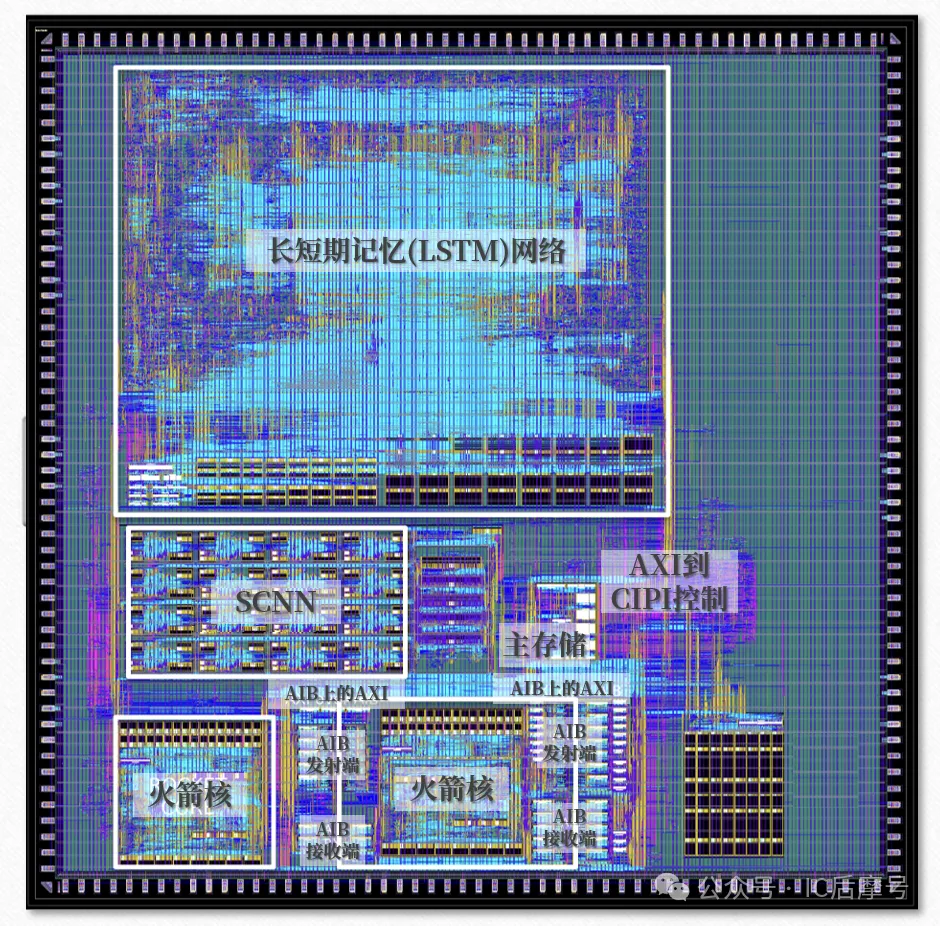

仿真设计采用富士通55nm LP制造工艺节点。下图显示芯片裸片照片(芯粒各部分和支撑结构以亮兰显示)。

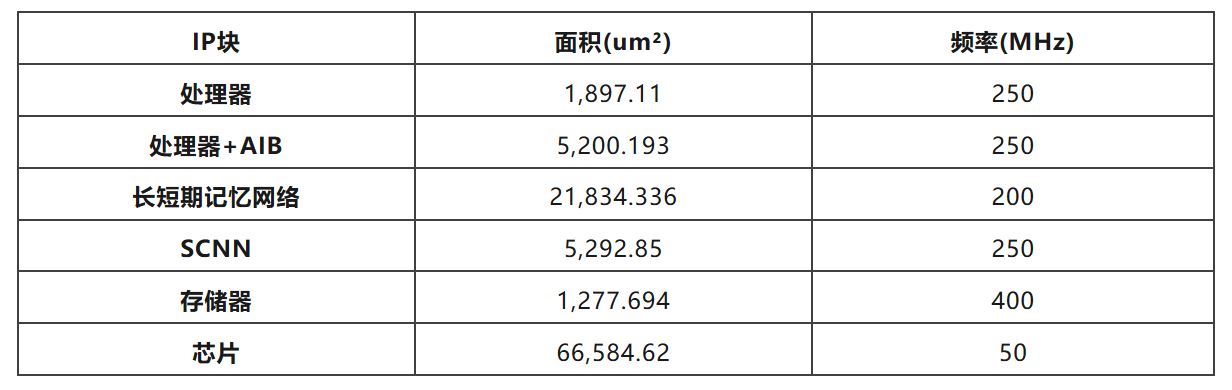

每个芯粒在隔离状态下运行的最低公共时钟频率为200 MHz。下表显示每个芯粒在隔离状态下的最高频率和面积。该芯粒组合在制造后,在1.2V数字电源电压(VDD)和25摄氏度的典型-典型工艺角下满足设计要求。

OpenOCD开源软件将树莓派3连接到JTAG接口,用于对CPU和片上存储器进行编程。该软件还为其他芯粒和片上存储器运行测试向量。每个芯粒都通过其JTAG接口进行了独立验证,系统则通过其中一个CPU的JTAG接口进行验证。结果是CPU和SCNN完全通过了测试向量验证,LSTM部分通过。

OpenOCD开源软件将树莓派3连接到JTAG接口,用于对CPU和片上存储器进行编程。该软件还为其他芯粒和片上存储器运行测试向量。每个芯粒都通过其JTAG接口进行了独立验证,系统则通过其中一个CPU的JTAG接口进行验证。结果是CPU和SCNN完全通过了测试向量验证,LSTM部分通过。

小结

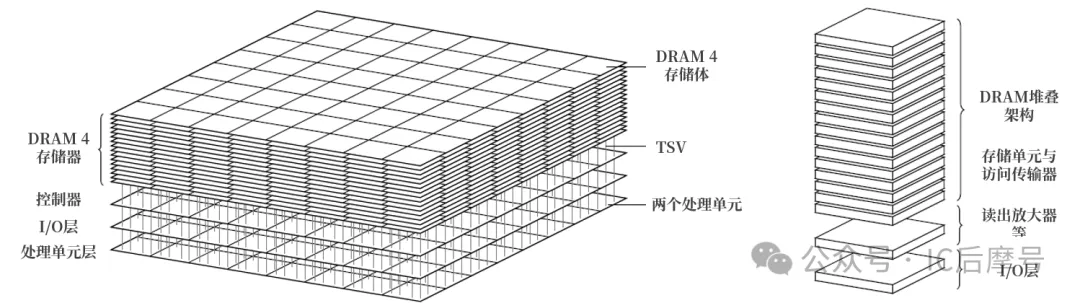

目前通常所说的“芯粒设计”,即为2.5D堆叠结构(3D垂直堆叠架构更像下图中的结构)。随着2.5D高密度重布线和TSV有源中介层技术的成熟,高性能计算系统设计在中介层上异构不同来源芯片(芯粒)的组合变得可行。

AI芯粒组合利用AIB互连协议来验证中介层上集成各种芯粒的可行性:芯粒组合由CPU和ML加速器组成。

采用2.5D堆叠与成熟的接口标准,进行CPU和LLM推理的芯粒组合:不仅改进了以往通过中介层连接现有芯片以突破光刻掩模版物理限制,而且允许更小的IO占用空间,减少了对IO数量的限制,使得数据总线具有更低的延迟和更高的带宽,并降低功耗。

参考文献

Joshua A. Stevens, Chiplet Set For Artificial Intelligence

S.Dey, An application specific processor architecture with 3d integration for recurrent neural networks