本文作者:AMD 工程师 Sowmya Ramakrishnan,文章来源:AMD开发者社区

本篇博文提供了有关 AMD Versal™ 自适应 SoC 中 eMMC 烧录和启动设置的技巧和指南。它还可用于调试 eMMC 烧录/启动失败。提交服务申请个案前,应先复查以下检查表。

1. AMD 是否支持对此 eMMC 闪存器件进行 Versal 启动和配置?

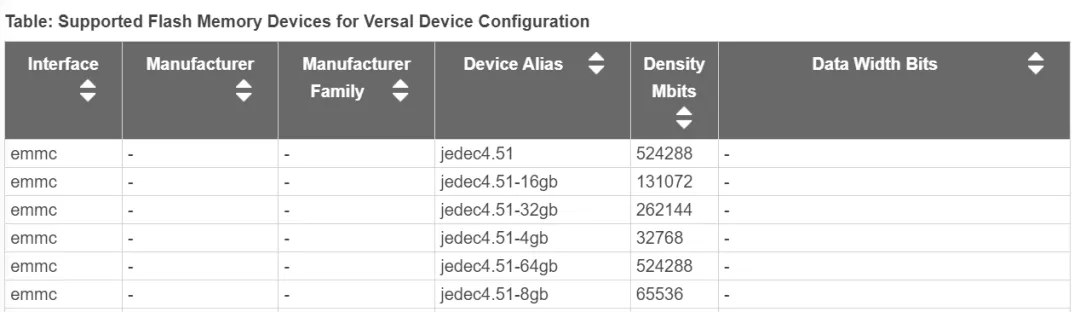

对于具有正式的业界规范的闪存器件(如 eMMC),我们遵循相应的规范版本来提供器件支持,而不是通过枚举每个特定制造商、制造商家族和器件的部件号来提供支持。这样即可在初始闪存选择以及长期设计维护方面为设计师提供广泛的可能性。

下表来自 UG908。Versal 中的 eMMC 接口支持 1.8V 下的 eMMC 规格版本 4.51。

https://docs.amd.com/r/en-US/ug908-vivado-programming-debugging/Versal-Configuration-Memory-Devices

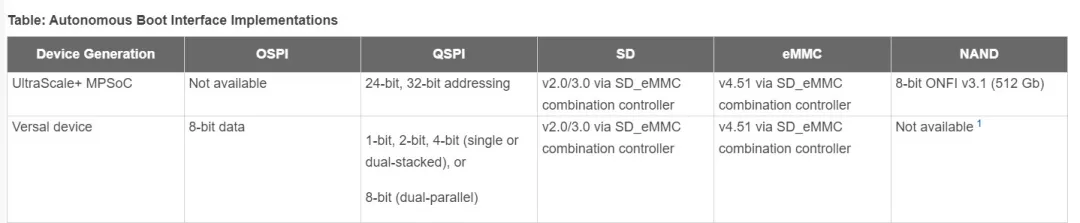

AMD Versal 和 AMD UltraScale+™ MPSoC 与其他先前架构之间的区别在于 Versal 中没有 NAND。eMMC1 模式取代了 NAND 模式,在提供相似性能的同时减少了管脚数。

下方设计咨询答复记录 (DAAR) 描述了在 eMMC 器件中观察到的一个问题,此类器件要求 CMD6 R1b 繁忙时间大于 1 ms,这导致主启动失败。

设计咨询答复记录 (DAAR) :

虽然目前在 Versal 器件中尚未报告任何操作失败,但认识此问题并查阅 Versal 的关联勘误表文档是非常重要的。

2. PCB 准则和硬件注意事项

下一步是检查 PCB 和开发板硬件。

AMD 参考板/评估板:

如果您当前使用的是 AMD 参考板,那么下列建议均已纳入考量。对于 AMD 参考板,建议运行 BEAM/BIT 工具以检查开发板/硬件完整性。请参阅相应产品指南以获取更多信息。您可跳至下一章节。

其他(定制)开发板:

UG863 中“SD/SDIO/eMMC”主题下的“eMMC”节包含 Versal 器件的印刷电路板 (PCB) 布局、设计考虑因素以及静态时序分析指南和公式。请确保您的定制 PCB 遵循 UG863 中列出的建议。 这些建议提供了有助于最大程度优化性能的准则。

UG863:

https://docs.amd.com/r/en-US/ug863-versal-pcb-design/SD/SDIO/eMMC

对于静态时序分析,在《DC 和 AC 开关特性》数据手册 (DS956-DS959) 的“PMC eMMC 控制器接口”章节中包含相应器件家族的 eMMC 接口的时序要求。DH0092 的“数据手册”部分列出了可用的 Versal 子家族。请务必参考适用于您的器件的数据手册。 另外,还应参考相应闪存的数据手册,确保时序得到满足。

DH0092:

https://docs.amd.com/v/u/en-US/dh0092-versal-boot-config

PCB 走线延迟取决于特定 PCB 的材料和走线宽度。

Issue 需要注意的是,为了确保 PCB 上的信号完整性正确无误,必须确保 Versal 器件的近端或远端没有任何反射。可以在 eMMC 时钟、命令和数据线路上布局 30 ohm 串联终端电阻器,并使其尽可能靠近 Versal 自适应 SoC。

出于信号完整性考量,请确保对 IBIS 模型仿真进行复查。时钟与数据信号完整性对于 eMMC 器件正常工作至关重要,运行速度越高,其重要性越高。

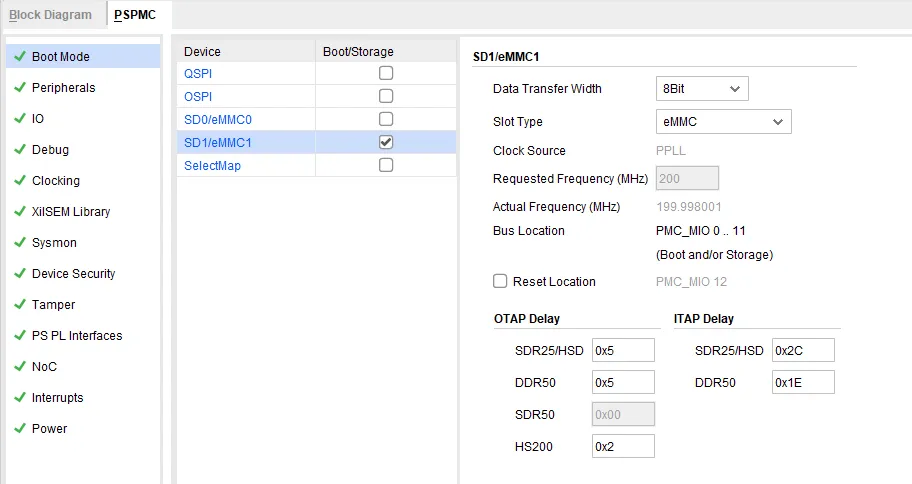

Versal 自适应 SoC 上有两个 SD_eMMC 控制器。SD_eMMC 控制器可用于 SD 或 eMMC 模式,它们互斥。SD_eMMC1 控制器用于 eMMC v4.51 启动模式。在 eMMC1 启动模式下,根据 REF_CLK 频率,RCU BootROM 以 8.7 MHz 到 19.3 MHz 之间的 eMMC1 器件时钟频率运行。eMMC1 启动模式支持 1.8V 以及 1 位、4 位和 8 位数据接口,时钟频率最高可达 200 MHz。BootROM 使用自动宽度检测来判定初始启动的数据总线宽度。自动总线宽度检测首先检查 8 位数据总线宽度,然后是 4 位数据总线宽度,最后是 1 位数据总线宽度。

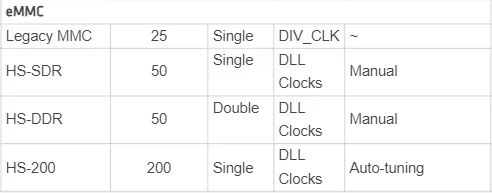

有三种操作模式:

25 MHz 下的传统 MMC 速度模式

50 MHz 下的高速 SDR 模式和 DDR 模式

200 MHz 下的 HS200 模式,数据率最高可达 1600 Mb/s

请复查《AM011》的 MIO 连接选项,确保遵循相关选项设置。若以 eMMC 作为主启动选项,须使用 PMC MIO Bank 500 的 MIO 0-11。

AM001:

https://docs.amd.com/r/en-US/am011-versal-acap-trm/PMC-MIO-Pin-Tables

SD_eMMC0 控制器不支持 eMMC 主启动。

3. MIO 和时钟配置

下一步是检查 MIO 和时钟配置。

MIO 配置

确保选中 SD1/eMMC1 启动模式,并确保将总线位置更改为 PMC MIO 0-11 以进行启动。

复位配置

控制器可以通过 PMC 复位控制器进行复位,或通过写入控制器的软件复位寄存器来复位。PMC 复位会影响整个控制器,并将所有寄存器设置为其复位默认状态。

可以使用 powercontrol [emmc_hwreset] 寄存器位来复位连接的 eMMC 卡。

时钟配置

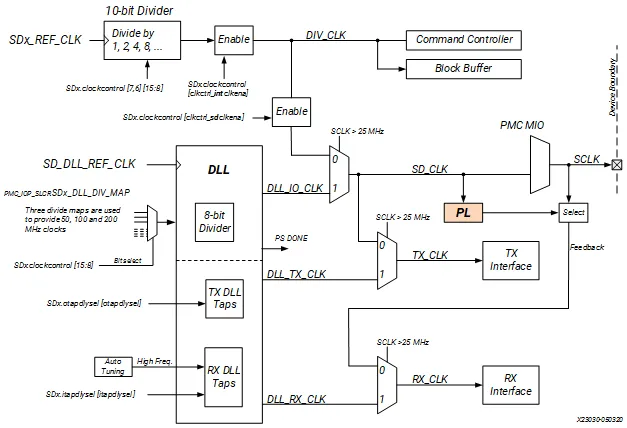

SD/eMMC 控制器具有以下三个从 PMC 时钟控制器接收的系统时钟:

用于 DIV_CLK 模块和控制器的 SDx_REF_CLK 参考时钟

用于 SD DLL 模块的 SD_DLL_REF_CLK 参考时钟

用于 AXI DMA 和编程接口的 PMC_IRO_CLK

控制器逻辑始终由 10 位分频器的 DIV_CLK 输出提供时钟,该分频器由 SDx_REF_CLK 参考时钟信号提供时钟。

然后,该控制器支持广泛的 I/O 时钟频率。

整体时钟架构图如下所示:

根据所需的 I/O 时钟频率,该控制器始终从以下两个可能的源之一来驱动 I/O 接口时钟 SDx_CLK:分别是来自时钟分频器的 DIV_CLK 和三个 DLL 模块时钟。

该控制器的 I/O 时钟模式为:

1.传统 MMC 速度与默认 MMC 速度相关。

2.默认情况下,eMMC 仅以传统 MMC 速度模式启动。软件驱动程序可以切换到高速模式以获得更高的吞吐量。

3.吞吐量基于 8 位 I/O 接口宽度。

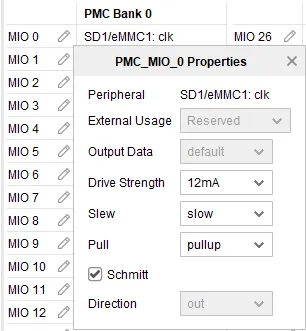

MIO 默认设置

在 Versal 器件中,使用的 MIO 采用以下默认设置。

默认驱动强度 (12 mA)

默认斜率 (slow)

默认弱上拉 (enabled)

启用 Schmitt 触发器输入

这些设置可在 AMD Vivado™ Design Suite 中更改。