作者:赵瑜斌Robin,来源:IC后摩号

由美国空军研究实验室(AFRL)和美国国家航空航天局(NASA)赞助的一款高性能航天计算(HPSC)处理器,基于芯粒的架构由波音公司为太空任务开发。

每个芯粒包含两个通过高级微控制器总线架构(AMBA)连接的四核 ARM Cortex-A53 CPU。这些芯粒可以通过不同的串行接口进行连接,为 AFRL 和 NASA 提供了一个灵活的平台,以满足各种潜在任务需求。

Content

高性能航天计算(HPSC)计划

太空任务"芯粒"多核处理器

空间处理器挑战

复杂任务与立方星计划

芯粒子系统

子系统建模仿真平台

双硬件测试平台

芯粒性能预估方法

1. 高性能空间计算计划

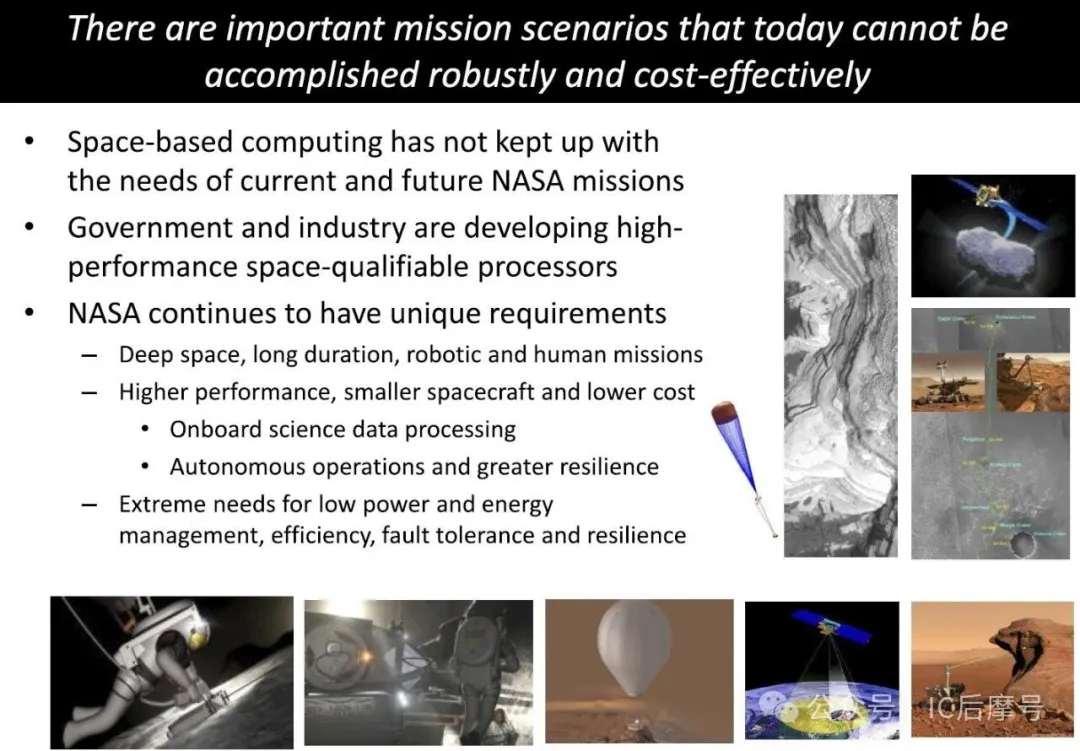

我们正从不断拓展太空探索和成就边界的科学领域,逐渐专项商业普惠领域。之前NASA 的新型“猎户座”飞船旨在将人类送往比以往更远的太空。詹姆斯·韦伯太空望远镜将深入太空,观测大爆炸后形成的首批星系。SpaceX 和蓝色起源,也致力于实现平民的太空飞行。而目前更大的商业目标是:卫星服务,从天气追踪、通信到国防的广泛应用。随着立方星和可重复使用火箭的出现,卫星正被快速且经济地送入太空。

NASA之需

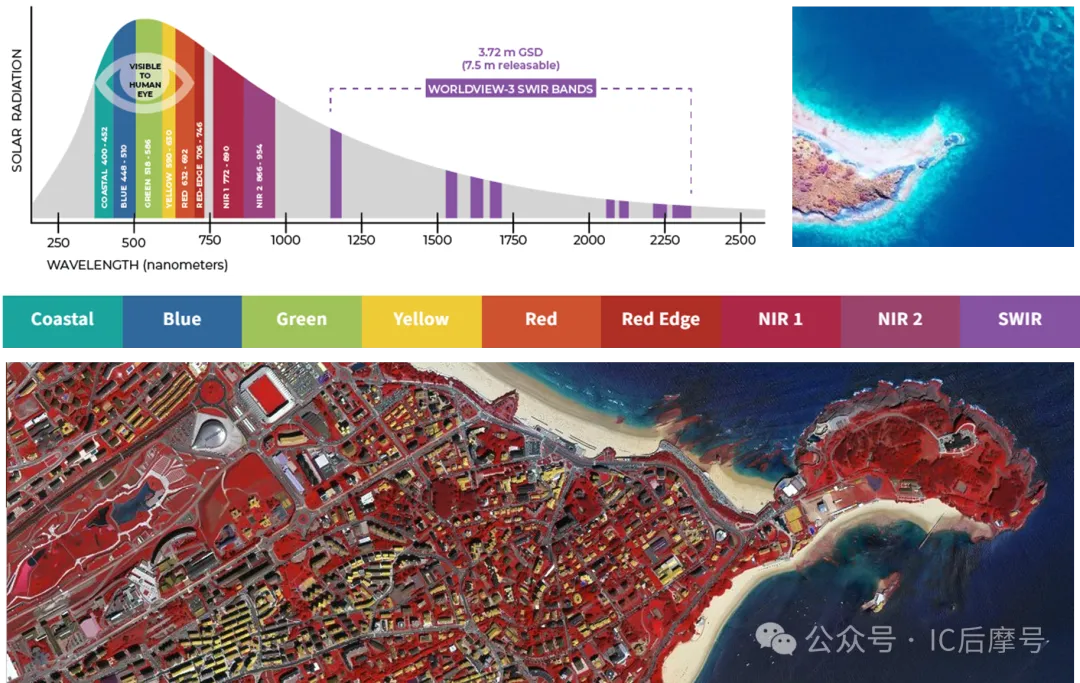

地球与太空之间的带宽极其有限,下行链路仅为每秒几百千比特,而传感器技术的不断进步又产生了更多需要处理的数据。为谷歌地图等提供图像的世界观测-4 号卫星,每天以 0.31 米的分辨率生成 68 万平方公里的图像。

航拍应用

然而,随着数据集变得越来越大,实时处理也变得越来越关键,太空计算机被要求具备强大的星载处理能力。

太空飞行计算多应用处理目标

NASA和AFRL启动的高性能航天计算(HPSC)计划,旨在打造满足多元任务性能和灵活性需求的多核处理器。

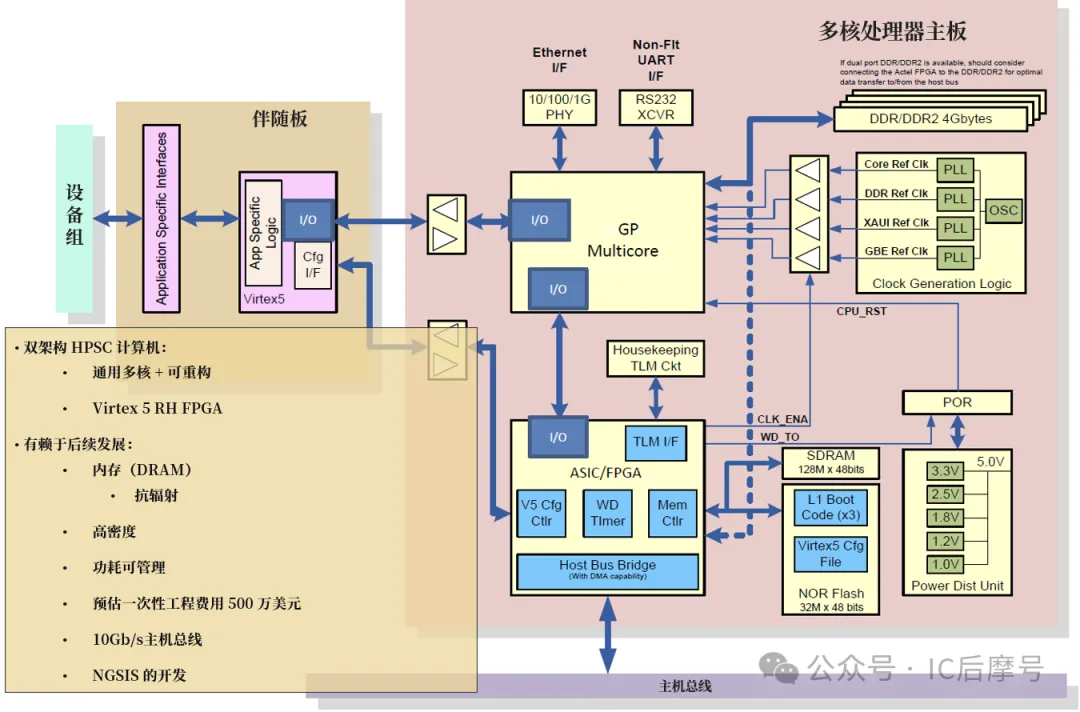

飞行计算系统参考设计

2017年波音公司因提出一个芯粒设计而获得合同,下图中的设计为太空任务提供了一个灵活的平台。一个芯粒可以连接到存储器、加速器(如 FPGA 或 GPU),以及其他芯粒相连。这种灵活性允许任务工程师根据任务需求更改系统配置,同时保持经过验证的中央处理器的稳定性。

波音公司芯粒架构设计

HPSC系统旨在为太空界提供超过十年的基石系统。而其设计平台本身需要数年才能终完成。对该双芯粒系统性能的预估,需要利用硬件基准测试,并确定跨芯粒并行化应用的最佳方式。

2. 空间处理器挑战

太空是一个以处理复杂任务而闻名的恶劣环境。任何太空计算机都面临着严峻的尺寸、重量和功耗限制。NASA为此立了立方星发射计划(CSLI),为教育机构和非营利组织提供了发射自己小型卫星的机会。这些立方星必须符合特定的尺寸标准,称为“U”,即 10×10×10 厘米。每个立方星可以是 1U、2U、3U 或 6U,通常每 U 重量小于 3 磅。此外,这些立方星只能为处理器提供几瓦的功率。

太空处理器还需要能够承受地面设施所没有的辐射影响。质子、中子和重离子可能撞击处理器,在系统中造成瞬时或永久性故障。这些故障被称为单粒子效应(SEE)。最常见的 SEE 类型是单粒子翻转(SEU)。

SEU 由粒子与晶体管碰撞引起,导致寄存器或存储单元内发生位翻转。在损坏程度最轻的情况下,受影响的晶体管可能保存未使用的数据,或者在该单元被写入新值后覆盖翻转位,从而有效地屏蔽了故障。在更严重的情况下,位翻转可能发生在系统的关键部分,例如程序计数器,这可能导致系统故障。

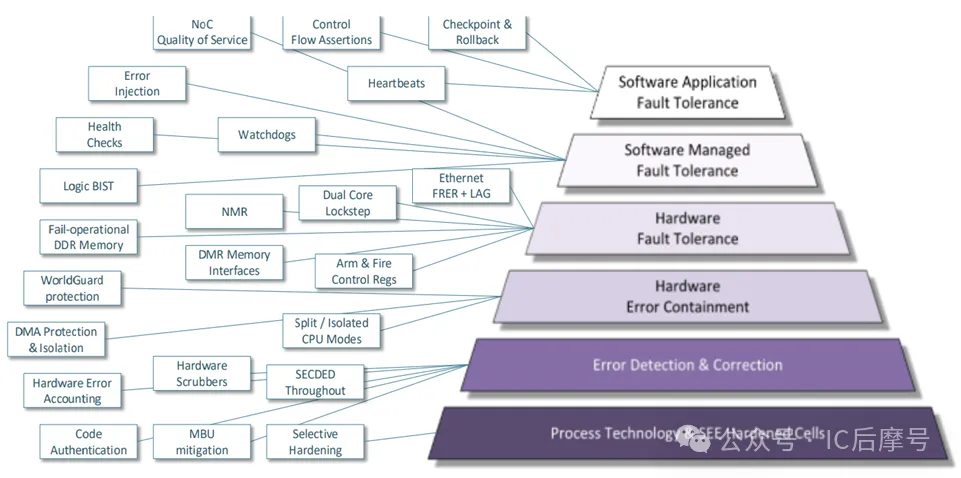

NASA HPSC容错体系

3. 芯粒子系统

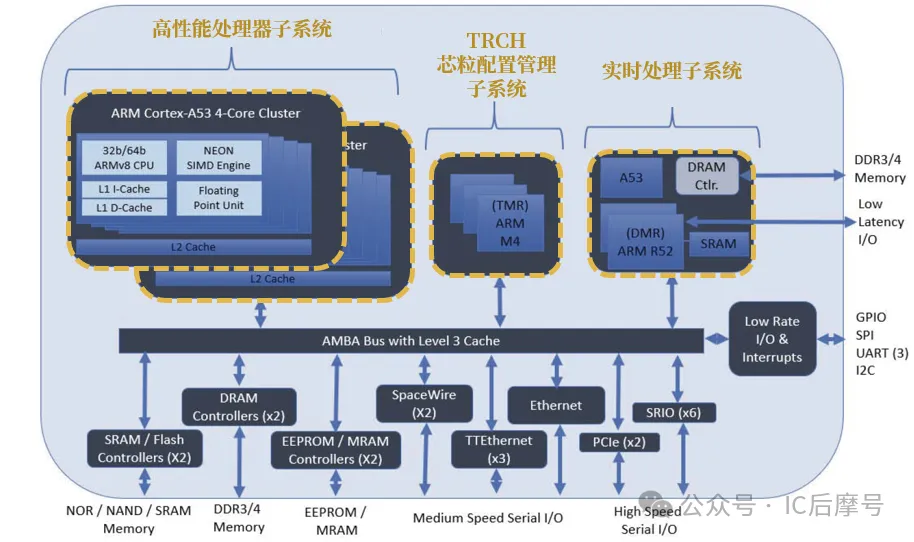

HPSC 芯粒由三个子系统组成,互相协同工作,在提供高性能的同时,保持太空所需的高可靠性。这些子系统通过带有三级缓存的高级微控制器总线架构(AMBA)相连。

第一个子系统是高性能处理子系统,包含两个四核 ARM Cortex-A53 集群。所有 ARM 内核都拥有 L1 缓存、一个浮点单元以及 ARM 的单指令多数据(SIMD)引擎 NEON。这些四核集群也通过 AMBA 总线相互通信。HPSC 处理器要求最低每秒 90 亿次操作(GOPS),目标为 15 GOPS,其中大部分将来自该子系统。NASA 和 AFRL 计划让高性能子系统以最高 800 MHz 的频率运行。

第二个子系统是芯粒配置管理子系统,由三个以三模冗余(TMR)方式运行的 ARM M4 内核组成。该系统将维护芯粒的健康状况,并以 TMR 方式运行以增强可靠性。

最后一个子系统是实时处理子系统,它有两个以双模冗余方式运行的 ARM R52 内核,与 SRAM 紧密耦合,此外还有一个 A53 内核和一个 DRAM 控制器。AMBA 总线还促进子系统与各种 I/O 和存储器控制器之间的通信。

下表列出 I/O 及其最大带宽。

串行 RapidIO(sRIO)基于 RapidIO 协议,是容错互连领域的领先标准;

PCI Express(PCIe)是主板连接外围设备(如图形卡、硬盘和网络接口卡)的常用接口;

SpaceWire 是用于航天器板载高速链路的标准;

时间触发以太网(TTE)是一种确定性协议,简化了具有内置可靠性功能的容错网络的设计。

在合成孔径雷达(SAR)项目中,大多数计算密集的应用,多芯粒平台能支持很好的扩展。采用两个芯粒相连,相比单个芯粒SAR预测加速为×1.93。

4. 硬件测试平台

用两个硬件测试平台来对 HPSC 的高性能处理子系统进行建模。机构目标是找到一个八核 ARM Cortex-A53 平台,并带有易于使用的串行端口来连接多个板卡。创建两个测试平台,建立了一个模型来结合基准测试结果,预估多芯粒的性能。

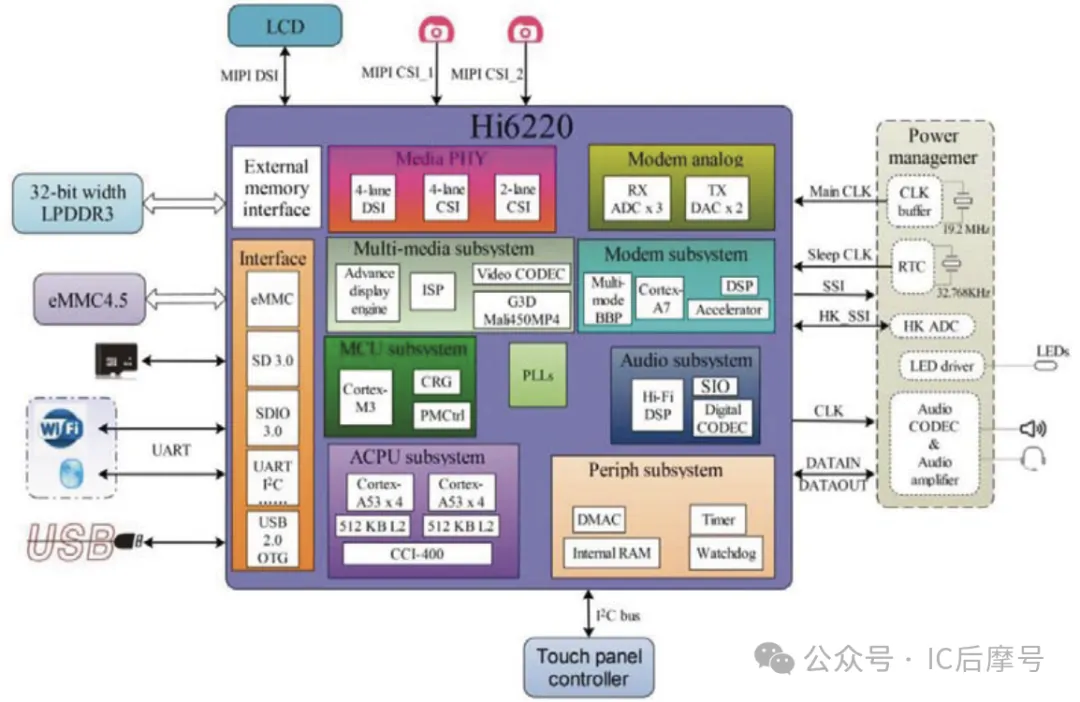

测试平台一,单独的 HiKey LeMaker 2GB 板,框图如图。该测试平台与单个芯粒非常相似。HiKey 是一款 ARMv8 架构开发板,有两个通过 CoreLink CCI-400 互连结构连接的四核 ARM Cortex-A53 内核,该互连结构基于 AMBA AXI4 规范。最大时钟频率为 1.2 GHz,板卡采用 32 位宽度的 DDR3 内存。

HiKey LeMaker 2GB 框图

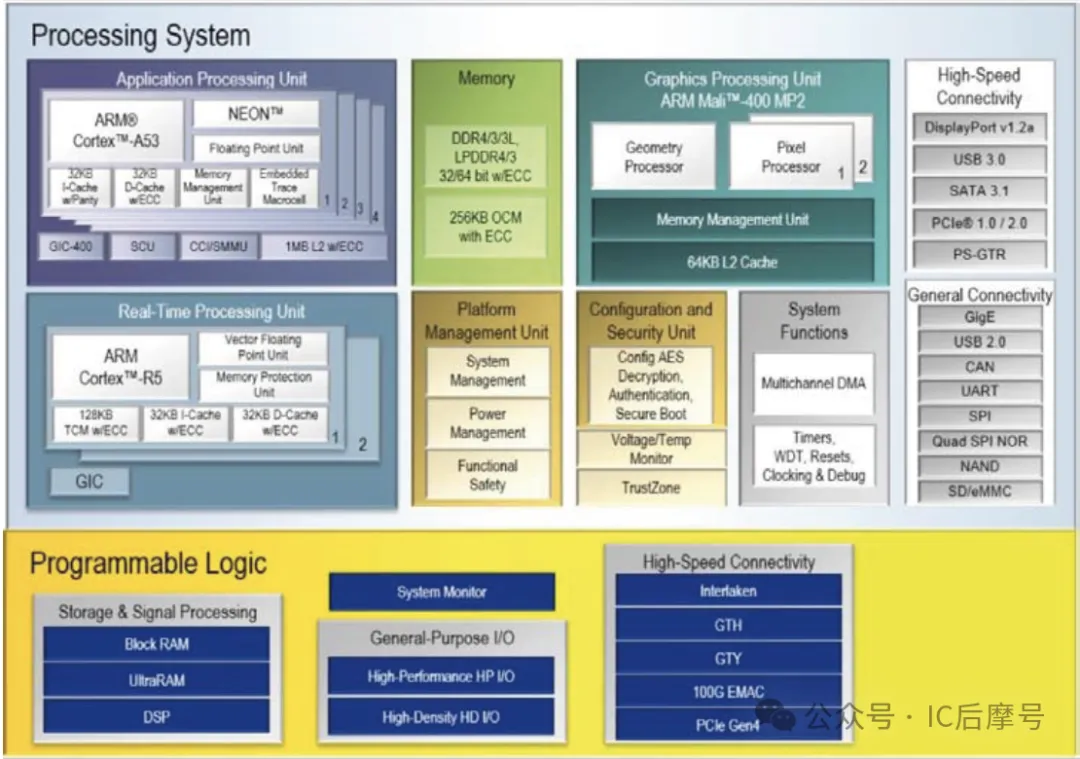

测试平台二,由两块 Xilinx ZCU102 评估板组成,每块都包含一个 Zynq UltraScale+ (US+) MPSoC 架构。该系统的框图如图 3 所示,通过千兆以太网(GigE)连接。

该平台帮助理解如何通过串行连接并行化应用,以及如何预估双芯粒的性能。开发板包括一个四核 ARM Cortex-A53 CPU、具有 64 位总线宽度的 DDR4 内存,以及一个千兆以太网端口。

Zynq UltraScale+框图

5. 芯粒性能预估

单芯粒性能评估

研究使用HiKey和US+平台来预估单芯粒性能,通过将四核性能乘以HiKey从四核到八核的性能变化百分比,来计算US+架构转换为带有AMBA总线的八核架构时的性能。取此项与 HiKey 八核性能之间的最短执行时间,来预估基准测试实例的芯粒运行时间。

芯粒运行时间=min(US4core×8coreHiKey/4coreHiKey, 8coreHiKey)

双芯粒性能预估

以太网性能,使用US+平台上的千兆以太网(GigE)接口进行基准测试。测量不同数据包大小下以太网的发送和接收时间。将应用跨芯粒分割时的实测性能与预估性能进行了比较。以太网开销的计算方法是将应用数据包大小(通过基准测试获得)的接收时间乘以需要执行该传输的次数,该次数与应用相关。

预估 US GigE 双板运行时间 = 单板运行时间 + 以太网开销

准确性=(实际运行时间 -预估运行时间 )/实际运行时间

模型的准确性因应用而异,

预估 GigE 双芯粒运行时间 = 单芯粒运行时间+以太网开销

计算跨多个芯粒的资源利用率(RU),其表示应用在多个计算资源(芯粒)上的扩展程度,

RU = 单芯粒运行时间 /(2×双芯粒运行时间 )×100%

预估双芯粒运行时间 = 单芯粒运行时间 + 通信开销

参考文献

Benjamin Schwaller, Emulation-based Performance Studies on the HPSC Space Processor

Next Generation Space Processor (NGSP) High Performance Spaceflight Computing (HPSC)