AMD在 ISE 2025 上推进沉浸式、自适应及智能音视频

judy 在 周四, 02/06/2025 - 10:25 提交

在 ISE 2025 上,AMD 将展示其多样化产品组合,这些产品组合支持多种 AV-over-IP、连接和视频处理应用,同时还支持基于 AI 的创新

在 ISE 2025 上,AMD 将展示其多样化产品组合,这些产品组合支持多种 AV-over-IP、连接和视频处理应用,同时还支持基于 AI 的创新

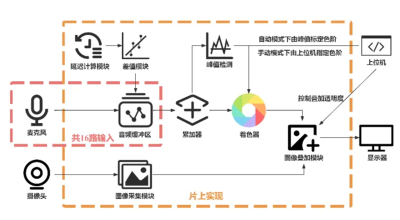

在 AMD FPGA 及自适应 SoC 器件的支持下,今年的优秀作品亮点纷呈,涵盖图像处理、人工智能、算法加速、机器控制等多个前沿领域。

最后一期我们主要介绍智多晶DDR Controller使用时的注意事项。

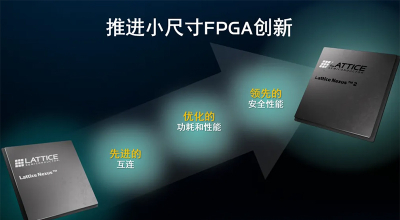

莱迪思半导体其下一代小型FPGA平台Lattice Nexus™ 2凭借其领先的低功耗和高性能、先进的连接性和安全特性荣获2025年BIG创新奖

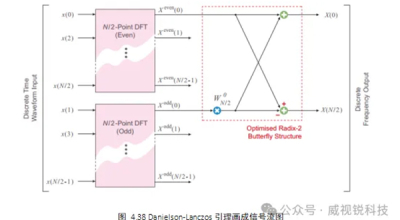

Danielson和Lanczos描述了一种利用DFT的周期性来减少计算需求的方法,即减少计算DFT所需的复乘子的数量。

本文诠释了为什么在今天的电子行业中更加需要使用VIP在验证环境中来改进调试、覆盖收敛和提升质量,以加快项目交付和增加投资回报

在技术飞速发展的今天,新兴的航空电子、关键基础设施和汽车应用正在重新定义人们对现场可编程门阵列(FPGA)的期望

FPGA 通常按照逻辑容量进行分类,这种方式固然简单,但未能充分体现现代 FPGA 作为可更改的片上系统所能提供的丰富功能和资源。

本期主要介绍智多晶DDR Controller的常见应用领域、内部结构、各模块功能、配置界面、配置参数等内容。

本应用手册可用于指导将 TPS65219 电源管理集成电路 (PMIC) 集成到为 Xilinx® Zynq® UltraScale+® 系列 MPSoC 供电的系统中