Virtex® UltraScale+™ HBM 使用心得(2)——性能

judy 在 周五, 07/22/2022 - 16:46 提交

在上一篇关于HBM的介绍中,详细介绍了HBM的架构和配置,这里再记录下HBM另一个重要的特性——性能。

在上一篇关于HBM的介绍中,详细介绍了HBM的架构和配置,这里再记录下HBM另一个重要的特性——性能。

Xilinx 7系列FPGA具有灵活的内部存储资源架构,可以可配置为各种不同的尺寸。本文详细解释了这一特性,并阐述了如何进行资源与性能之间的权衡取舍。

利用 UART IP 以及 AXI Interrupt Contriller IP 实现通过串口发送数据产生中断,控制器接收到中断并将串口发送出来的数据重新通过串口打印出来

最近在xilinx Virtex® UltraScale+™系列的芯片上使用了HBM,发现相比传统的DDR,还是有很多不错的地方,这里对HBM的使用做一个简单的总结。

相较三星传统SSD固态硬盘,CPU利用率可高达97%,处理时间减少逾50%,功耗降低70%。

tcl对于文件的操作还是比较强大的,通过一些命令可以对文件进行一些操作。

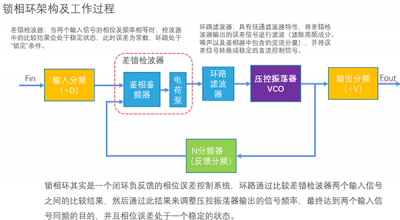

锁相环是一种控制反馈电路。PLL对时钟网络进行系统级别的时钟管理和偏移控制,具有时钟倍频、分频、相位偏移和可编程占空比的功能

电子设备无处不在,其中很多都通过开放的未加密 TCP/IP 通道连接。在这样的环境下,安全成为重大隐忧。

tcl中的控制和C语言差距不大,包括if、while、for、foreach、switch、break、continue等。

通过 AXI GPIO 检测按键状态产生中断信号,中断控制器检测到中断后,给处理器发送中断请求