给Vivado Block Design的TCL脚本添加IP repository (仓库) 路径信息

judy 在 周五, 05/20/2022 - 13:25 提交

在Vivado里,可以从Block Design导出TCL脚本,保存工程。之后可以从TCL脚本恢复工程。导出的TCL脚本中,可能不包含用户IP的路径信息

在Vivado里,可以从Block Design导出TCL脚本,保存工程。之后可以从TCL脚本恢复工程。导出的TCL脚本中,可能不包含用户IP的路径信息

本文主要介绍时钟及I/O规划的各个阶段及流程要点。

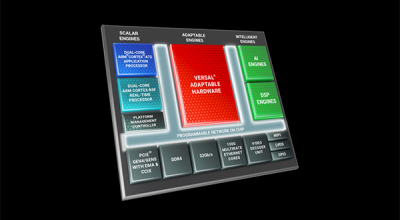

AMD收购赛灵思的目的在于将其差异化IP集成到公司未来旗下的CPU中,Xilinx无论是从丰富的计算引擎还是其AI引擎技术都能让AMD在服务器CPU市场上扩大影响力

Kria KR260 入门套件能够快速开发用于机器人和工业自动化的硬件加速应用。与基于 GPU 的解决方案相比,带来显著的生产力、单位功耗性能提升和时延下降

本直播将为您详细介绍在 AI Benchmark 的测试中能达到90%以上的计算效率的 AI 芯片,以及如何使用 VCK5000 加速 AI计算的设计方法和设计资源。

采用任意精度数据类型,可以在获得相同精度的运算条件下,运算速度更快且使用更少的资源。

本文我们介绍FPGA外设DDR2/DDR3硬件设计相关内容,包括PCB板层数估计,信号端接、信号完整性及时序考虑等问题。

本文描述在 Versal® ACAP 中实现电源排序的各种方法。

该视频介绍了电源域和电源状态的概念,以及如何在您的设计中使用 Ultra96 实现电源域切换。

本文我们通过一个具体的实例,演示HLS设计流程。