Vitis 2022.1 现已推出!

judy 在 周五, 05/13/2022 - 09:40 提交

Vitis 统一软件平台 2022.1现已推出!

Vitis 统一软件平台 2022.1现已推出!

Vivado® ML 2022.1 在 Vivado ML 标准安装中可支持 Versal Premium VP1202、VP1502、VP1702 和 VP1802 器件。

搭载赛灵思 Zynq RFSoC 架构的 Evenstar RU 使用相同的基础硬件即可提供能够满足广泛应用需求的灵活性,包括4G/5G、毫米波和 sub-6GHz。

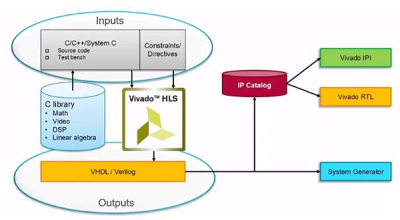

传统的FPGA RTL设计流程主要是采用VHDL、VerilogHDL或System Verilog进行工程的开发,同时也是通过硬件描述语言来编写测试案例对开发的工程进行仿真验证

本视频描述了使用频率调整优化单位功率性能,以及频率调整方法及其权衡。

SEM IP在上板调试过程中有时会出现一些错误, 比如无法执行IP的插错纠错功能; 或者自身的初始化无法完成等等, 需要对SEM IP本身进行调试定位

FIFO是FPGA设计中最常用的IP,读写时序相对简单,可能正是因为这个原因,通常不会去细读FIFO手册,具体怎么操作大概清楚,上手就写,一般不会出什么问题。最近却遇到读FIFO异常的情况,特意记录一下

该视频介绍了 Power Islands 及其 API 的概念。

以下是在 Vitis™ 软件平台中创建 Platform Loader and Manager (PLM) elf 文件的步骤。在 Versal™ 器件中,PLM 在 PMC 内执行,并用于引导 APU 和 RPU。

Power Advantage Tool 用于监控设计中的功耗。本视频介绍了如何设置 Ultra96,并提供了在其他评估板上的设置链接。