FPGA+GPU+CPU国产化人工智能平台

judy 在 周三, 01/08/2025 - 15:21 提交

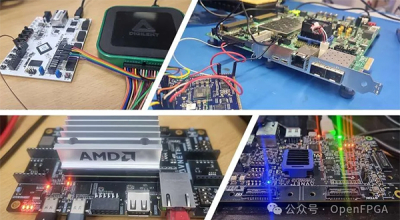

平台采用国产化FPGA+GPU+CPU构建嵌入式多核异构智算终端,可形成FPGA+GPU、FPGA+CPU、CPU+GPU等组合模式

平台采用国产化FPGA+GPU+CPU构建嵌入式多核异构智算终端,可形成FPGA+GPU、FPGA+CPU、CPU+GPU等组合模式

实现时序收敛的关键要素之一是确保我们编写出能够充分利用设备架构特性和实现工具功能的优质代码。让我们来看看可以帮助我们提供更好质量代码的几个方面。

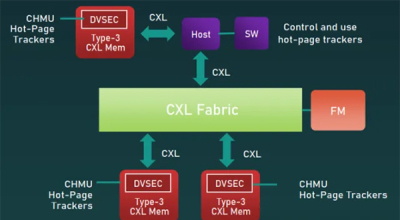

第二代 AMD Versal Premium 系列提供了全新水平的存储器和数据带宽,具备 CXL® 3.1、PCIe® Gen6 和 DDR5/LPDDR5X 接口功能

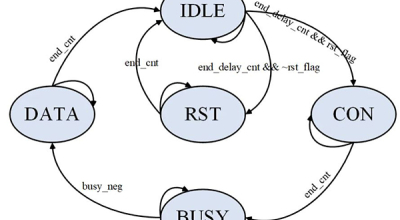

在本文中,我们将继续探讨,介绍如何用SystemC实现完整的AXI4协议,以实现DMA的测试。

今天要分享的是一个简单的MIPI到LVDS(DVP)接口转换的案例。目的就是要把低成本FPGA的应用潜力充分利用起来。

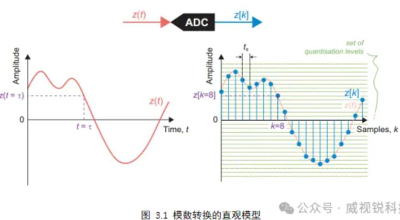

将模拟信号转换为数字等效信号时发生的两个过程分别是采样和量化。可以将采样视为将信号的时间轴转换为一组离散时刻

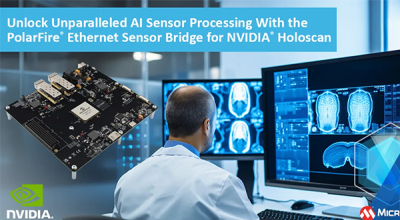

PolarFire®以太网传感器桥接器携手NVIDIA® Holoscan来啦!它超节能、协议转换溜到飞起,还自带高安全性与SEU免疫力!

很多FPGA厂商都在自己EDA工具里嵌入IP减少FPGA项目的开发周期,使用 IP 是一种有助于实现按时、高质量且经济高效的项目交付的方法

Compute Express Link 规范的最新发布旨在优化监控和管理并增强操作系统和应用程序的功能,同时扩展安全性

前文讲解了AD7606的功能及原理,本文通过FPGA实现AD7606的并行接口数据采集,对应时序如下所示