FPGA实现SDRAM接口(2)--初始化

judy 在 周四, 12/12/2024 - 10:17 提交

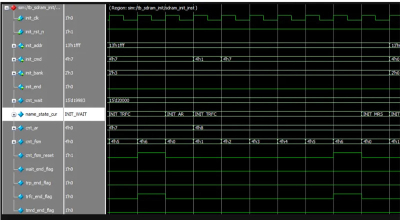

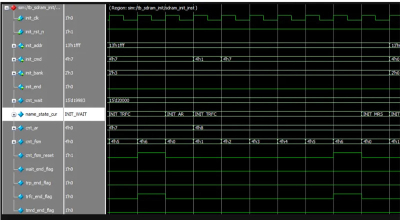

SDRAM 的初始化是芯片上电后必须进行的一项操作,只有进行了初始化操作的 SDRAM 芯片才可被正常使用

SDRAM 的初始化是芯片上电后必须进行的一项操作,只有进行了初始化操作的 SDRAM 芯片才可被正常使用

全新推出莱迪思Nexus 2下一代小型FPGA平台、发布莱迪思Avant 30和Avant 50系列器件扩展中端产品组合、增强了针对特定应用的解决方案集合和设计软件工具的功能

客户需要采购一个基于FPGA的电子系统,该系统要足够小巧,能够装入手持式便携箱中

全新 AMD Vitis 统一软件平台 2024.2 版本已于近期推出。系统架构师和开发人员可以借助新版本进一步提升其设计开发流程,同时提高整体系统性能。

本文将详细介绍FPGA分频器的设计方法,并附上Verilog代码示例,以供参考

该系列器件采用先进互连架构,搭配出色外设以及高质量散热封装,为您的成本敏感型应用带来卓越性能。选择适合您当前和未来需求的器件。

HuaPro P3的软硬件系统可支持自动化和智能化的实现流程、支持灵活模块化扩展和云部署,能提供高性能硬件验证

高云 Arora V 25K 产品,内部资源丰富,具有全新架构的高性能 DSP,集成一个MIPI DPHY TX/RX 硬核(2.5Gbps)

7系列IO模块相关的结构如图1所示,前文对IOB、IDELAYE2、ILOGIC、OLOGIC进行了讲解,还剩下ISERDESE2、OSERDESE2、ODELAYE2原语