【视频】基于所关注的区域 (ROI) 的编码演示:软件架构

judy 在 周二, 12/01/2020 - 09:47 提交

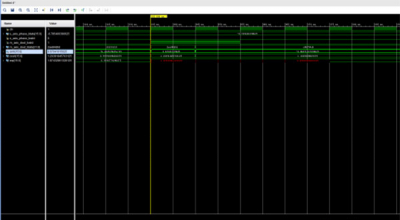

详细了解基于 Zynq UltraScale+ MPSoC 视频编解码器单元 (VCU) ROI 的编码参考设计的软件架构。 首先,我们将讨论 Xilinx 视频和连接 IP 支持堆栈, 接着,视频将描述 VCU ROI 应用程序的软件堆栈,并详细讨论 Gstreamer 流输出管道、以及 ROI GStreamer 插件和 Gstreamer 流输入管道。 最后将介绍用于启动参考设计的资源。