Vivado 仿真器:我能在 Vivado 中从 VHDL 项目运行时序仿真吗?

judy 在 周五, 11/26/2021 - 10:05 提交

我在 Vivado 中有个 VHDL 项目。 UG900 用户指南指出: “后综合和后实现时序仿真仅就 Verilog 提供支持。不支持 VHDL 时序仿真。” 这是否意味着我不能在 VHDL 项目中运行时序仿真? 该项目有没有运行时序仿真的办法?

我在 Vivado 中有个 VHDL 项目。 UG900 用户指南指出: “后综合和后实现时序仿真仅就 Verilog 提供支持。不支持 VHDL 时序仿真。” 这是否意味着我不能在 VHDL 项目中运行时序仿真? 该项目有没有运行时序仿真的办法?

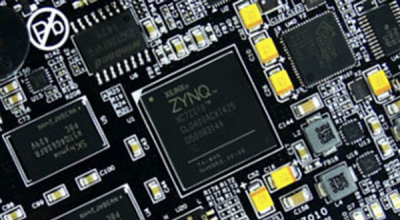

在编写ZYNQ的FPGA逻辑代码过程中,往往需要对时序进行分析。时序信号的分析一般通常有软件仿真和在线仿真两种,本文介绍这两种方法的具体使用方法。

如何存储关键数据的方法,属于规模测试验证的手段,但对于Verilog的调试过程还不够直观,因为无法确切地了解Verilog代码仿真中各个关联信号是如何作用的。Verilog的确可以像C/C++一样启动调试模式,针对每行代码进行调试。但请注意,由于Verilog是并行执行的,而仿真是采用delta时间逐步并行推进的,采用代码调试较为困难,所以常常需要存储全部或部分仿真数据,这就是波形文件。