构建自定义 AXI4-Stream FIR 滤波器

judy 在 周四, 11/07/2024 - 09:52 提交

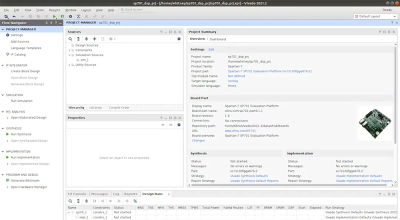

AMD-Xilinx 的 Vivado 开发工具具有很多方便FPGA开发功能,我最喜欢的功能之一是block design的设计流程

AMD-Xilinx 的 Vivado 开发工具具有很多方便FPGA开发功能,我最喜欢的功能之一是block design的设计流程

AXI4 STREAM DATA FIFO也是一种先入先出形式的数据缓存队列

Vivado在打包IP核的时候提供了AXI4-Stream的接口,接下来分别例化两个IP

该系列先对AXI4-Stream协议及其使用做一个简单的介绍

本文主要介绍使用AXI4S(AXI4-Stream)接口的视频IP细节。

本文介绍如何自己编写AXI4-Stream slave类型的图像源。

本视频描述了使用 INTERFACE 指令指定 AXI4-Stream 接口的过程。

如果说要在AXI、AXI-Lite、AXI-Stream中选一种最喜欢的类型,我选择Stream总线,因为这是最简单的类型,而且使用起来非常方便,五个通道就剩数据传输,就像网络通信中的TCP与UDP,UDP用起来更简洁。

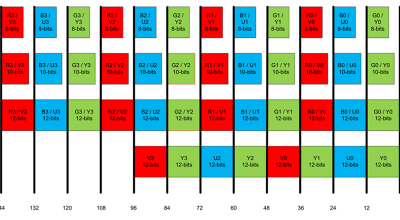

AXI4-Stream协议是一种用来连接需要交换数据的两个部件的标准接口,它可以用于连接一个产生数据的主机和一个接受数据的从机。当然它也可以用于连接多个主机和从机。该协议支持多种数据流使用相同共享总线集合,允许构建类似于路由、宽窄总线、窄宽总线等更为普遍的互联。比较重要的信号线有:

ACLK: 时钟源,全局时钟信号。所有信号在ACLK信号上升沿采样。